Other Parts Discussed in Thread: TIDM-HV-1PH-DCAC, PMP23338

我按照TIDM-HV-1PH-DCAC 的文档去配置驱动

驱动配置如下

EALLOW;

CpuSysRegs.PCLKCR0.bit.TBCLKSYNC = 0;// Disable TBCLK within the EPWM

//****************************************************************

EPwm1Regs.TBCTL.bit.PRDLD = TB_SHADOW;//The period register (TBPRD) is loaded from its shadow register

EPwm1Regs.TBPRD = INV_u16PERIOD;

EPwm1Regs.TBCTR = 0x00;

EPwm1Regs.TBPHS.bit.TBPHS = 0x00;

EPwm1Regs.TBCTL.bit.CTRMODE = TB_COUNT_UPDOWN; //

EPwm1Regs.TBCTL.bit.HSPCLKDIV = 0x0; // TBCLK = EPWMCLK / (HSPCLKDIV x CLKDIV).

EPwm1Regs.TBCTL.bit.CLKDIV = 0x0;

EPwm1Regs.CMPA.bit.CMPA = 0;

EPwm1Regs.CMPCTL.bit.SHDWAMODE = CC_SHADOW;

EPwm1Regs.CMPCTL.bit.LOADAMODE = CC_CTR_ZERO;

EPwm1Regs.AQCTLA.all = 0;

EPwm1Regs.AQCTLA.bit.CAU = AQ_CLEAR;

EPwm1Regs.AQCTLA.bit.CAD = AQ_SET;

EPwm1Regs.DBCTL.bit.DEDB_MODE = 0;

EPwm1Regs.DBRED.all = INV_u16DBBAND;

EPwm1Regs.DBFED.all = INV_u16DBBAND;

EPwm1Regs.DBCTL.bit.OUT_MODE = DB_FULL_ENABLE;

EPwm1Regs.DBCTL.bit.IN_MODE = DBA_ALL;

EPwm1Regs.DBCTL.bit.POLSEL = DB_ACTV_HIC;//

EPwm1Regs.TBCTL.bit.PHSEN = TB_DISABLE; //

EPwm1Regs.EPWMSYNCOUTEN.bit.ZEROEN = 1;

SyncSocRegs.SYNCSELECT.bit.SYNCOUT = 1;

//****************************************************************

//****************************************************************

EPwm1Regs.ETSEL.bit.SOCAEN = 1; // Enable SOC on A group

EPwm1Regs.ETSEL.bit.SOCASEL = 1; // Select SOC from from CPMA on upcount

EPwm1Regs.ETPS.bit.SOCAPRD = CTRL_u16ISR_FREQ_RATIO; // Generate pulse on 1st event

//****************************************************************

//****************************************************************

EPwm2Regs.TBCTL.bit.PRDLD = TB_SHADOW;

EPwm2Regs.TBPRD = INV_u16PERIOD;

EPwm2Regs.TBCTR = 0x00;

EPwm2Regs.TBPHS.bit.TBPHS = 0x00;

EPwm2Regs.TBCTL.bit.CTRMODE = TB_COUNT_UPDOWN;

EPwm2Regs.TBCTL.bit.HSPCLKDIV = 0x0;

EPwm2Regs.TBCTL.bit.CLKDIV = 0x0;

EPwm2Regs.CMPA.bit.CMPA = 0;

EPwm2Regs.CMPCTL.bit.SHDWAMODE = CC_IMMEDIATE;

EPwm2Regs.CMPCTL.bit.LOADAMODE = CC_CTR_ZERO;

EPwm2Regs.AQCTLA.all = 0;

EPwm2Regs.AQCTLA.bit.CAD = 1;//01: Clear: force EPWMxA output low.

// EPwm2Regs.AQCTLA.bit.CAU = AQ_CLEAR;//AQ_NO_ACTION;

// EPwm2Regs.AQCTLA.bit.CAD = AQ_NO_ACTION;

// EPwm2Regs.AQCTLA.bit.ZRO = AQ_NO_ACTION;

EPwm2Regs.DBCTL.bit.DEDB_MODE = 0;

EPwm2Regs.DBRED.all = INV_u16DBBAND;//1831;// INV_PWM_DEADBAND;//上升沿死区时钟数

EPwm2Regs.DBFED.all = INV_u16DBBAND;//1831;// INV_PWM_DEADBAND;//下降沿死区时钟数

EPwm2Regs.DBCTL.bit.OUT_MODE = DB_FULL_ENABLE;//

EPwm2Regs.DBCTL.bit.IN_MODE = DBA_ALL;

EPwm2Regs.DBCTL.bit.POLSEL = DB_ACTV_HIC;//EPWMxB is inverted

EPwm2Regs.TBCTL.bit.PHSEN = TB_ENABLE;

EPwm2Regs.TBPHS.bit.TBPHS = 0x02;

EPwm2Regs.EPWMSYNCINSEL.bit.SEL = SYNC_IN_SRC_SYNCOUT_EPWM1;

EPwm2Regs.TBCTL.bit.PHSDIR = TB_UP;

CpuSysRegs.PCLKCR0.bit.TBCLKSYNC = 1;// enable TBCLK within the EPWM

EDIS;然后在中断ISR中更新驱动占空比

如下

EPwm1Regs.CMPA.bit.CMPA = u16InvCmp;

EPwm2Regs.CMPA.bit.CMPA = 1;

if(duty >= 0.0f){

EPwm1Regs.AQCTLA.bit.CAU = 2;//10: Set: force EPWMxA output high.

EPwm1Regs.AQCTLA.bit.CAD = 3;//11: Toggle EPWMxA output:

EPwm1Regs.AQCTLA.bit.ZRO = 1;//01: Clear: force EPWMxA output low.

EPwm2Regs.AQCTLA.bit.CAD = 1;//01: Clear: force EPWMxA output low.

}else{

EPwm1Regs.AQCTLA.bit.CAU = 1;//01: Clear: force EPWMxA output low.

EPwm1Regs.AQCTLA.bit.CAD = 3;//11: Toggle EPWMxA output:

EPwm1Regs.AQCTLA.bit.ZRO = 2;//10: Set: force EPWMxA output high.

EPwm2Regs.AQCTLA.bit.CAD = 2;//10: Set: force EPWMxA output high.

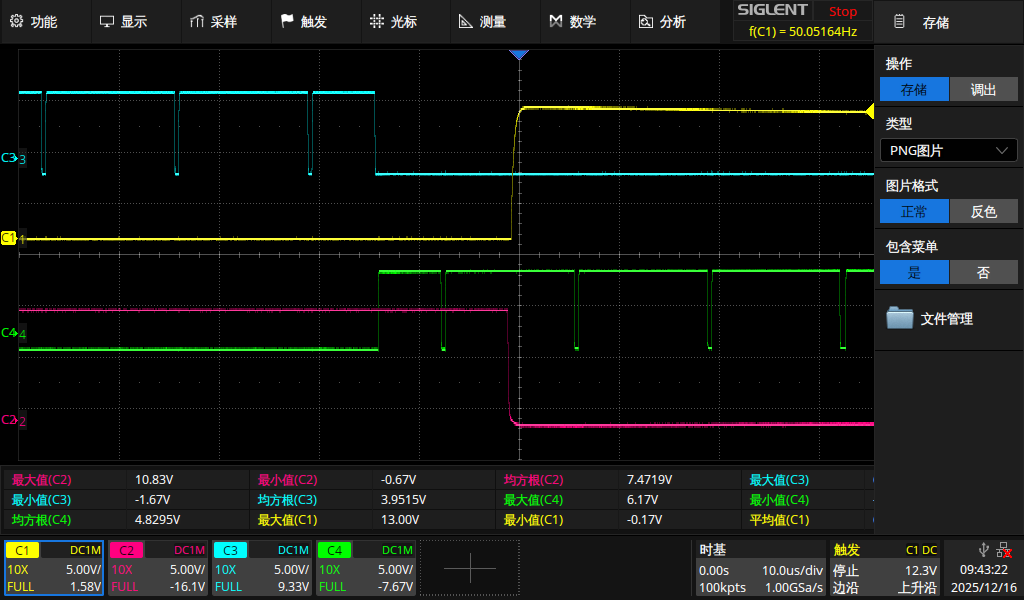

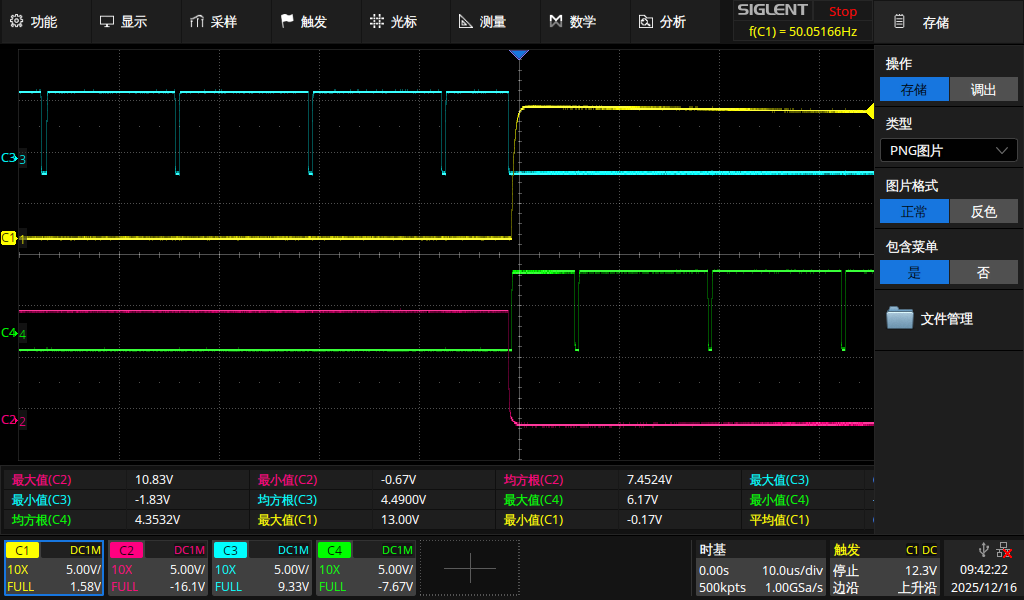

}但是开环测试发现过零点驱动异常

图片如下

其中

绿色为PWM1A(快管上管)

蓝色为PWM1B(快管下管)

紫色为PWM2A(慢管上管)

黄色为PWM2B(慢管下管)

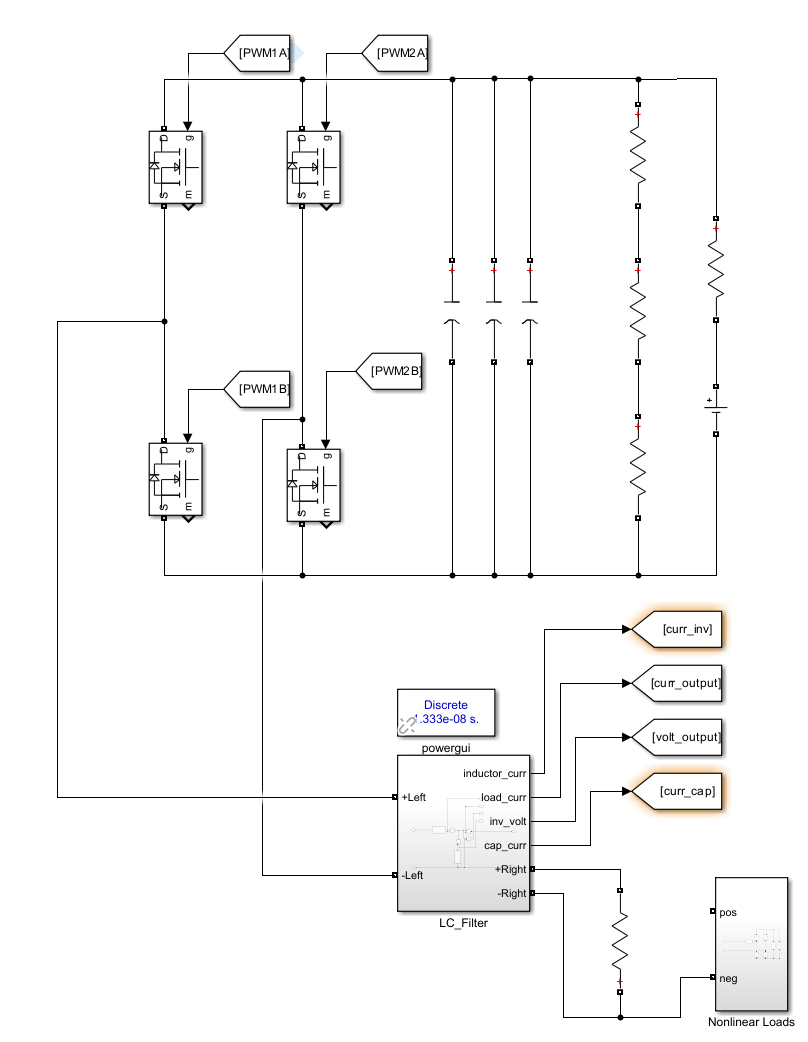

拓扑结构

如下:

问题

如下:

问题1:快管在过零点处驱动占空比异常(少了一半)

问题2:慢管和快管之间的延时(有时蓝色关断,黄色很快置高;有时蓝色关断后,黄色延时一段时间才置高)