问题1:时钟周期的真实大小

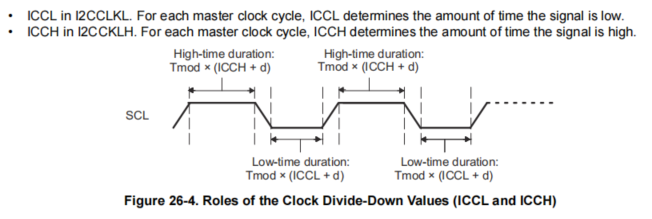

用户手册中关于ICCL和ICCH的描述是高电平和低电平的持续时间,并不包含上升下降沿,那是否说明,假设存在较缓慢的边沿,实际上会导致I2C信号的频率发生改变?(就不能用手册上面给的公式进行计算了)

问题2:I2C输出高低电平大小

手册上面提到I2C基于的标准是NXP2.1,其中高电平的范围是在0.7VDD~VDD+0.5V,但是实测出来在3.3V供电的情况下,实测出来为3.47V~3.9V,与协议标准存在一定偏差。

综合以上两个问题,想请教一下各位专家,谢谢。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

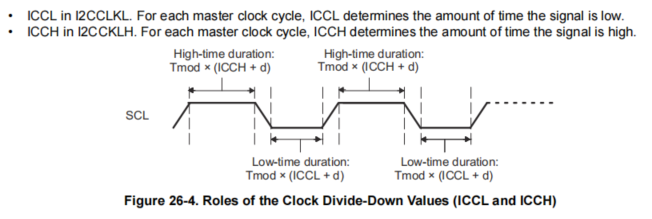

问题1:时钟周期的真实大小

用户手册中关于ICCL和ICCH的描述是高电平和低电平的持续时间,并不包含上升下降沿,那是否说明,假设存在较缓慢的边沿,实际上会导致I2C信号的频率发生改变?(就不能用手册上面给的公式进行计算了)

问题2:I2C输出高低电平大小

手册上面提到I2C基于的标准是NXP2.1,其中高电平的范围是在0.7VDD~VDD+0.5V,但是实测出来在3.3V供电的情况下,实测出来为3.47V~3.9V,与协议标准存在一定偏差。

综合以上两个问题,想请教一下各位专家,谢谢。

您好

假设存在较缓慢的边沿,实际上会导致I2C信号的频率发生改变?

有意思的假设,假设情况下会,实际上一般不会出现。

但是实测出来在3.3V供电的情况下,实测出来为3.47V~3.9V,

哪个是实测值?

您好

那是不是就可以理解成DSP的I2C配置确实是这样工作的,只关注高低电平时间?

datasheet给出的是示意,方便您去理解应用,至于高低电平时间确实重要,但是不是“只”关注,因为干扰等均会影响,只是程度不同而已。

3.47~3.9V是实测值。以3.3V供电为例,期望的高电平范围应该在2.31V~3.8V

在范围里就可以,因为只是为了识别高低电平。

您好

同时第一个问题,那存在一个较缓慢的上升沿情况下,先不考虑干扰等其他问题,那实际上每个周期的偏差,基本就在高低电平判断中间的那块区域,所对应的时间?

您这个问题一般都是外因引起的,所以如上所说是干扰等引起,排除干扰等外因即可,理论上存在实际可能性很低(没有外部影响的话)。

第二个问题的话,我理解3.9V已经超过协议标准的上限了(3.8V),在这种情况下,会导致什么异常现象发生吗

超过时就存在无法准确识别高电平,这个可能影响您的运行(如果涉及高电平的部分)。

您好

针对第一个问题如上的回复,排除您外部干扰问题,您及多个设备的话,这是本身的信号问题,并不是单是上升沿的延迟,而是多个设备存在信号传递的延迟,这个不是纠结于沿的延迟,而是考虑多个设备对时钟信号是否能达到同步的问题。您看到的延迟是现象,而本质是时钟信号在多个设备上由于电路物理意义上的远近导致的不足。建议考虑这部分方向来进行优化。

第二个问题根据您之前的实测显示大部分在这个范围内,您高于这个范围只是影响识别高电平的时间,如果您有这部分应用需要识别高电平的完整有可能受影响,这个可以通过程序进行辅助优化。