请教

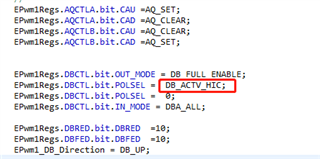

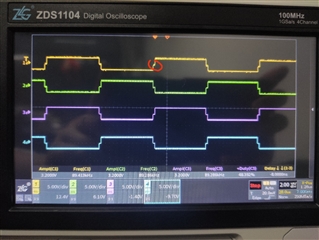

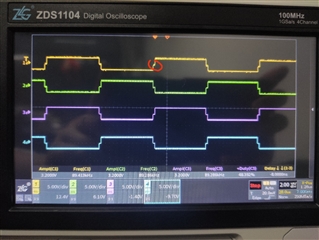

想得到epwm1、epwm2都是带死区的高电平互补有效,将epwm1和epwm2的极性都设置为HIC时(如上图),输出的pwm波有小台阶,如下图,小台阶表示什么,是我哪设置的不对吗?

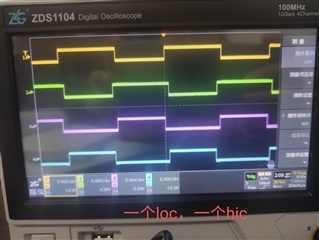

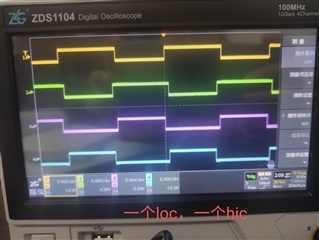

我试了一下, epwm1设置为 EPwm1Regs.DBCTL.bit.POLSEL = DB_ACTV_LOC; epwm2设置为 EPwm2Regs.DBCTL.bit.POLSEL = DB_ACTV_HIC; 波形很好,没有小台阶,如下图

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

请教

想得到epwm1、epwm2都是带死区的高电平互补有效,将epwm1和epwm2的极性都设置为HIC时(如上图),输出的pwm波有小台阶,如下图,小台阶表示什么,是我哪设置的不对吗?

我试了一下, epwm1设置为 EPwm1Regs.DBCTL.bit.POLSEL = DB_ACTV_LOC; epwm2设置为 EPwm2Regs.DBCTL.bit.POLSEL = DB_ACTV_HIC; 波形很好,没有小台阶,如下图

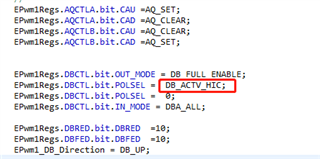

额,比较好奇你在代码中为什么在

EPwm1Regs.DBCTL.bit.POLSEL = DB_ACTV_HIC;

后面又加了一句

EPwm1Regs.DBCTL.bit.POLSEL = 0;

对寄存器两次赋值可能会有问题,不知道你的实验2是不是也是这样写寄存器的?

谢谢您的回复,不好意思,贴错代码了,两个设置都没有EPwm1Regs.DBCTL.bit.POLSEL = 0;这一行

两组设置

① EPwm1Regs.DBCTL.bit.POLSEL = DB_ACTV_HIC; EPwm2Regs.DBCTL.bit.POLSEL = DB_ACTV_HIC;

②EPwm1Regs.DBCTL.bit.POLSEL = DB_ACTV_LOC; EPwm2Regs.DBCTL.bit.POLSEL = DB_ACTV_HIC;

其余设置均相同,不知道为什么①波形有个小台阶,而②波形正常

有没有测试过PWM1和PWM3搭配的情况下会有同样问题吗?

没看到过相关资料说明不能两个同时设置为DB_ACTV_HIC的,而且似乎运行结果的波形也没有出现死区。

#include "F28x_Project.h"

Uint32 EPwm1TimerIntCount;

Uint32 EPwm3TimerIntCount;

void InitEPwm1Example(void);

void InitEPwm3Example(void);

void main(void)

{

InitSysCtrl();

CpuSysRegs.PCLKCR2.bit.EPWM1=1;

CpuSysRegs.PCLKCR2.bit.EPWM3=1;

InitEPwm1Gpio();

InitEPwm3Gpio();

DINT;

InitPieCtrl();

IER = 0x0000;

IFR = 0x0000;

InitPieVectTable();

EALLOW;

EDIS;

EALLOW;

CpuSysRegs.PCLKCR0.bit.TBCLKSYNC =0;

EDIS;

InitEPwm1Example();

InitEPwm3Example();

EALLOW;

CpuSysRegs.PCLKCR0.bit.TBCLKSYNC =1;

EDIS;

EPwm1TimerIntCount = 0;

EPwm3TimerIntCount = 0;

EINT; // Enable Global interrupt INTM

ERTM; // Enable Global realtime interrupt DBGM

for(;;)

{

asm (" NOP");

}

}

void InitEPwm1Example()

{

EPwm1Regs.TBPRD = 140; // Set timer period

EPwm1Regs.TBPHS.bit.TBPHS = 0x0000; // Phase is 0

EPwm1Regs.TBCTR = 0x0000; // Clear counter

EPwm1Regs.TBCTL.bit.CTRMODE = TB_COUNT_UPDOWN;

EPwm1Regs.TBCTL.bit.PHSEN = TB_DISABLE; // Disable phase loading

EPwm1Regs.TBCTL.bit.CLKDIV = 0;

EPwm1Regs.TBCTL.bit.HSPCLKDIV =1; // Clock ratio to SYSCLKOUT

EPwm1Regs.TBSTS.all = 0;

EPwm1Regs.CMPCTL.bit.SHDWAMODE = CC_SHADOW;

EPwm1Regs.CMPCTL.bit.SHDWBMODE = CC_SHADOW;

EPwm1Regs.CMPCTL.bit.LOADAMODE = CC_CTR_ZERO;

EPwm1Regs.CMPCTL.bit.LOADBMODE = CC_CTR_ZERO;

EPwm1Regs.CMPA.bit.CMPA = 70;

//

// Set actions

//

EPwm1Regs.AQCTLA.bit.CAU =AQ_SET;

EPwm1Regs.AQCTLA.bit.CAD =AQ_CLEAR;

EPwm1Regs.AQCTLB.bit.CAU =AQ_CLEAR;

EPwm1Regs.AQCTLB.bit.CAD =AQ_SET;

EPwm1Regs.AQSFRC.all = 0;

EPwm1Regs.AQCSFRC.all = 0;

EPwm1Regs.DBCTL.bit.OUT_MODE = DB_FULL_ENABLE;

EPwm1Regs.DBCTL.bit.POLSEL = DB_ACTV_HIC;

EPwm1Regs.DBCTL.bit.IN_MODE = DBA_ALL;

EPwm1Regs.DBRED.bit.DBRED =10;

EPwm1Regs.DBFED.bit.DBFED =10;

}

void InitEPwm3Example()

{

EPwm3Regs.TBCTL.bit.CLKDIV = 0;

EPwm3Regs.TBCTL.bit.HSPCLKDIV =1; // Clock ratio to SYSCLKOUT'

EPwm3Regs.TBCTL.bit.CTRMODE = 2;

EPwm3Regs.TBCTL.bit.PHSEN = 0; // Disable phase loading

EPwm3Regs.TBSTS.all = 0;

EPwm3Regs.TBPHS.bit.TBPHS = 0; // Phase is 0

EPwm3Regs.TBCTR = 0; // Clear counter

EPwm3Regs.TBPRD = 140; // Set timer period

EPwm3Regs.TBSTS.all = 0;

EPwm3Regs.CMPCTL.bit.SHDWAMODE = CC_SHADOW;

EPwm3Regs.CMPCTL.bit.SHDWBMODE = CC_SHADOW;

EPwm3Regs.CMPCTL.bit.LOADAMODE = CC_CTR_ZERO;

EPwm3Regs.CMPCTL.bit.LOADBMODE = CC_CTR_ZERO;

EPwm3Regs.CMPA.bit.CMPA = 70;

EPwm3Regs.AQCTLA.bit.CAU =AQ_SET;

EPwm3Regs.AQCTLA.bit.CAD =AQ_CLEAR;

EPwm3Regs.AQCTLB.bit.CAU =AQ_CLEAR;

EPwm3Regs.AQCTLB.bit.CAD =AQ_SET;

EPwm3Regs.AQSFRC.all = 0;

EPwm3Regs.AQCSFRC.all = 0;

EPwm3Regs.DBCTL.bit.OUT_MODE = DB_FULL_ENABLE;

EPwm3Regs.DBCTL.bit.POLSEL = DB_ACTV_HIC;

EPwm3Regs.DBCTL.bit.IN_MODE = DBA_ALL;

EPwm3Regs.DBRED.bit.DBRED = 10;

EPwm3Regs.DBFED.bit.DBFED = 10;

}

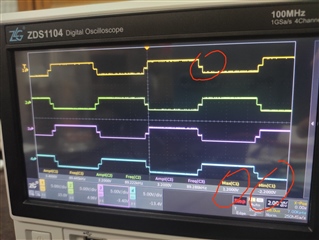

您好,PWM1和PWM3搭配也会出现同样的问题,代码已上传,

设置为EPwm1Regs.DBCTL.bit.POLSEL = DB_ACTV_HIC; EPwm3Regs.DBCTL.bit.POLSEL = DB_ACTV_HIC时波形如图不知道代码哪块有问题,可以这个波形驱动MOS管吗?

不理解为什么pwm波出现了正电压和负电压,怎样才能设置为只有正电压和0电压呢?

你好,不知道你的测试点是在哪里。我怀疑是否跟你的后端有关,因为芯片本身是不可能输出负的电压的。

能不能尝试将芯片引脚的后端电路断开后再测试引脚上的波形?