Other Parts Discussed in Thread: TIDM-DC-DC-BUCK

这是我的CMPSS

void CMPSS_Init(Uint16 base1,Uint16 u16DacHigh,Uint16 u16DacLow)

{

// Enable CMPSS1

CMPSS_enableModule(base1);

// Use VDDA as the reference for comparator DACs

CMPSS_configDAC(base1,CMPSS_DACVAL_SYSCLK |CMPSS_DACREF_VDDA |CMPSS_DACSRC_SHDW);

// Set DAC to H and L values

CMPSS_setDACValueHigh(base1, u16DacHigh);

// Make sure the asynchronous path compare high and low event

// does not go to the OR gate with latched digital filter output

// hence no additional parameter CMPSS_OR_ASYNC_OUT_W_FILT is passed

// comparator oputput is "not" inverted for high compare event

CMPSS_configHighComparator(base1, CMPSS_INSRC_DAC);

// Comparator output is inverted for for low compare event

CMPSS_configFilterHigh(base1, 2, 10, 7);

// Reset filter logic & start filtering

CMPSS_initFilterHigh(base1);

// Configure CTRIPOUT path

CMPSS_configOutputsHigh(base1, CMPSS_TRIP_FILTER | CMPSS_TRIPOUT_FILTER);

// Comparator hysteresis control , set to 2x typical value

CMPSS_setHysteresis(base1, 0);

// Clear the latched comparator events

CMPSS_clearFilterLatchHigh(base1);

}

这是CBC模式配置代码

HWREG(EPWMXBAR_BASE + XBAR_O_TRIP4MUX0TO15CFG) = 0x0000;

HWREG(EPWMXBAR_BASE + XBAR_O_TRIP4MUX16TO31CFG) = 0x0000;

HWREG(EPWMXBAR_BASE + XBAR_O_TRIP4MUXENABLE) = 0x0000;

HWREG(EPWMXBAR_BASE + XBAR_O_TRIP5MUX0TO15CFG) = 0x0000;

HWREG(EPWMXBAR_BASE + XBAR_O_TRIP5MUX16TO31CFG) = 0x0000;

HWREG(EPWMXBAR_BASE + XBAR_O_TRIP5MUXENABLE) = 0x0000;

HWREG(EPWMXBAR_BASE + XBAR_O_TRIP7MUX0TO15CFG) = 0x0000;

HWREG(EPWMXBAR_BASE + XBAR_O_TRIP7MUX16TO31CFG) = 0x0000;

HWREG(EPWMXBAR_BASE + XBAR_O_TRIP7MUXENABLE) = 0x0000;

HWREG(EPWMXBAR_BASE + XBAR_O_TRIP8MUX0TO15CFG) = 0x0000;

HWREG(EPWMXBAR_BASE + XBAR_O_TRIP8MUX16TO31CFG) = 0x0000;

HWREG(EPWMXBAR_BASE + XBAR_O_TRIP8MUXENABLE) = 0x0000;

HWREG(EPWMXBAR_BASE + XBAR_O_TRIP9MUX0TO15CFG) = 0x0000;

HWREG(EPWMXBAR_BASE + XBAR_O_TRIP9MUX16TO31CFG) = 0x0000;

HWREG(EPWMXBAR_BASE + XBAR_O_TRIP9MUXENABLE) = 0x0000;

HWREG(EPWMXBAR_BASE + XBAR_O_TRIP10MUX0TO15CFG) = 0x0000;

HWREG(EPWMXBAR_BASE + XBAR_O_TRIP10MUX16TO31CFG) = 0x0000;

HWREG(EPWMXBAR_BASE + XBAR_O_TRIP10MUXENABLE) = 0x0000;

HWREG(EPWMXBAR_BASE + XBAR_O_TRIP11MUX0TO15CFG) = 0x0000;

HWREG(EPWMXBAR_BASE + XBAR_O_TRIP11MUX16TO31CFG) = 0x0000;

HWREG(EPWMXBAR_BASE + XBAR_O_TRIP11MUXENABLE) = 0x0000;

// CMPSS2

//XBAR_EPWM_MUX00_CMPSS1_CTRIPH

XBAR_setEPWMMuxConfig(XBAR_TRIP4, XBAR_EPWM_MUX00_CMPSS1_CTRIPH);

// Enable Mux 0 to generate TRIP4

XBAR_enableEPWMMux(XBAR_TRIP4, XBAR_MUX00);

// CMPSS5

//XBAR_EPWM_MUX08_CMPSS5_CTRIPH

XBAR_setEPWMMuxConfig(XBAR_TRIP5, XBAR_EPWM_MUX08_CMPSS5_CTRIPH);

// Enable Mux 0 to generate TRIP5

XBAR_enableEPWMMux(XBAR_TRIP5, XBAR_MUX08);

// Trip 4 is the input to the DCAHCOMPSEL

EPWM_selectDigitalCompareTripInput(EPWM1_BASE,EPWM_DC_TRIP_TRIPIN4,EPWM_DC_TYPE_DCAH);

// Trigger event when DCBH is high

EPWM_setTripZoneDigitalCompareEventCondition(EPWM1_BASE,EPWM_TZ_DC_OUTPUT_A2,EPWM_TZ_EVENT_DCXH_HIGH);

// 设置DCB的路径为异步非滤波

EPWM_setDigitalCompareEventSource(EPWM1_BASE,EPWM_DC_MODULE_A,EPWM_DC_EVENT_2,EPWM_DC_EVENT_SOURCE_ORIG_SIGNAL);

//! 设置数字比较输入同步模式。

EPWM_setDigitalCompareEventSyncMode(EPWM1_BASE,EPWM_DC_MODULE_A,EPWM_DC_EVENT_2,EPWM_DC_EVENT_INPUT_SYNCED);

EPWM_selectDigitalCompareTripInput(EPWM6_BASE,EPWM_DC_TRIP_TRIPIN5,EPWM_DC_TYPE_DCAH);

// Trigger event when DCBH is high

EPWM_setTripZoneDigitalCompareEventCondition(EPWM6_BASE,EPWM_TZ_DC_OUTPUT_A2,EPWM_TZ_EVENT_DCXH_HIGH);

// 设置DCB的路径为异步非滤波

EPWM_setDigitalCompareEventSource(EPWM6_BASE,EPWM_DC_MODULE_A,EPWM_DC_EVENT_2,EPWM_DC_EVENT_SOURCE_ORIG_SIGNAL);

//! 设置数字比较输入同步模式。

EPWM_setDigitalCompareEventSyncMode(EPWM6_BASE,EPWM_DC_MODULE_A,EPWM_DC_EVENT_2,EPWM_DC_EVENT_INPUT_SYNCED);

EPWM_enableTripZoneSignals(EPWM1_BASE,EPWM_TZ_SIGNAL_DCAEVT2);

EPWM_enableTripZoneSignals(EPWM6_BASE,EPWM_TZ_SIGNAL_DCAEVT2);

EPWM_setTripZoneAction(EPWM1_BASE, EPWM_TZ_ACTION_EVENT_TZA, EPWM_TZ_ACTION_LOW);

EPWM_setTripZoneAction(EPWM6_BASE, EPWM_TZ_ACTION_EVENT_TZA, EPWM_TZ_ACTION_LOW);

// 设置DCB CBC

EPWM_clearTripZoneFlag(EPWM1_BASE, EPWM_TZ_FLAG_DCAEVT2);

EPWM_clearTripZoneFlag(EPWM6_BASE, EPWM_TZ_FLAG_DCAEVT2);

EPWM_clearTripZoneFlag(EPWM1_BASE, EPWM_TZ_FLAG_CBC);

EPWM_clearTripZoneFlag(EPWM6_BASE, EPWM_TZ_FLAG_CBC);

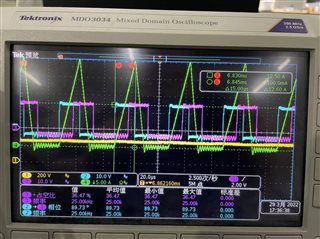

这是加入CBC配置后开关频率由50K 180°交错 改变为25K 90°交错。波形图如下