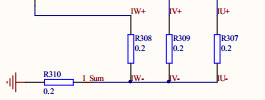

用DSP28035 控制永磁同步电机做过流或短路保护,ADC模块的comparator模块的三个比较器的正向输入端,分别采样电机U、V、W三相电流,负向输入端使用内部的DAC,当出现过流时,三个比较器的的输出低电平触发EPWM封锁PWM输出。

现在问题是,当U相过流或短路时,COMP1OUT输出低电平,只能封锁U相EPWM1A和EPWM1B输出低电平。

当V相过流或短路时,COMP2OUT输出低电平,只能封锁V相EPWM2A和EPWM2B输出低电平。

当W相过流或短路时,COMP3OUT输出低电平,只能封锁W相EPWM3A和EPWM3B输出低电平。

我现在想当其中任何一相过流时,使6路PWM都输出低电平,怎么操作。

EPWM部分程序设置如下:

// Init PWM Digital Compare Control Register for EPWM1-EPWM3

EPwm1Regs.DCTRIPSEL.bit.DCAHCOMPSEL = DC_COMP3OUT; // DCAH = Comparator 3 output

EPwm1Regs.TZDCSEL.bit.DCAEVT1 = TZ_DCAH_LOW; // DCAEVT1 = DCAH low(will become active as Comparator output goes low)

EPwm1Regs.DCACTL.bit.EVT1SRCSEL = DC_EVT1; // DCAEVT1 = DCAEVT1 (not filtered)

EPwm1Regs.DCACTL.bit.EVT1FRCSYNCSEL = DC_EVT_ASYNC; // Take async path

EPwm1Regs.DCTRIPSEL.bit.DCBHCOMPSEL = DC_COMP3OUT; // DCBH = Comparator 3 output

EPwm1Regs.TZDCSEL.bit.DCBEVT1 = TZ_DCBH_LOW; // DCBEVT1 = DCBH low(will become active as Comparator output goes low)

EPwm1Regs.DCBCTL.bit.EVT1SRCSEL = DC_EVT2; // DCBEVT1 = DCBEVT1 (not filtered)

EPwm1Regs.DCBCTL.bit.EVT1FRCSYNCSEL = DC_EVT_ASYNC; // Take async path

// Init PWM Digital Compare Control Register for EPWM1-EPWM3

EPwm2Regs.DCTRIPSEL.bit.DCAHCOMPSEL = DC_COMP1OUT; // DCAH = Comparator 1 output

EPwm2Regs.TZDCSEL.bit.DCAEVT1 = TZ_DCAH_LOW; // DCAEVT1 = DCAH low(will become active as Comparator output goes low)

EPwm2Regs.DCACTL.bit.EVT1SRCSEL = DC_EVT1; // DCAEVT1 = DCAEVT1 (not filtered)

EPwm2Regs.DCACTL.bit.EVT1FRCSYNCSEL = DC_EVT_ASYNC; // Take async path

EPwm2Regs.DCTRIPSEL.bit.DCBHCOMPSEL = DC_COMP1OUT; // DCBH = Comparator 1 output

EPwm2Regs.TZDCSEL.bit.DCBEVT1 = TZ_DCBH_LOW; // DCBEVT1 = DCBH low(will become active as Comparator output goes low)

EPwm2Regs.DCBCTL.bit.EVT1SRCSEL = DC_EVT2; // DCBEVT1 = DCBEVT1 (not filtered)

EPwm2Regs.DCBCTL.bit.EVT1FRCSYNCSEL = DC_EVT_ASYNC; // Take async path

// Init PWM Digital Compare Control Register for EPWM1-EPWM3

EPwm3Regs.DCTRIPSEL.bit.DCAHCOMPSEL = DC_COMP2OUT; // DCAH = Comparator 2 output

EPwm3Regs.TZDCSEL.bit.DCAEVT1 = TZ_DCAH_LOW; // DCAEVT1 = DCAH low(will become active as Comparator output goes low)

EPwm3Regs.DCACTL.bit.EVT1SRCSEL = DC_EVT1; // DCAEVT1 = DCAEVT1 (not filtered)

EPwm3Regs.DCACTL.bit.EVT1FRCSYNCSEL = DC_EVT_ASYNC; // Take async path

EPwm3Regs.DCTRIPSEL.bit.DCBHCOMPSEL = DC_COMP2OUT; // DCBH = Comparator 2 output

EPwm3Regs.TZDCSEL.bit.DCBEVT1 = TZ_DCBH_LOW; // DCBEVT1 = DCBH low(will become active as Comparator output goes low)

EPwm3Regs.DCBCTL.bit.EVT1SRCSEL = DC_EVT2; // DCBEVT1 = DCBEVT1 (not filtered)

EPwm3Regs.DCBCTL.bit.EVT1FRCSYNCSEL = DC_EVT_ASYNC; // Take async path

// Init Trip Zone Select Register

// Enable DCAEVT1 and DCBEVT1 are one shot trip sources

// Note: DCxEVT1 events can be defined as one-shot.

// DCxEVT2 events can be defined as cycle-by-cycle.

EPwm1Regs.TZSEL.bit.DCAEVT1 = 1;

EPwm1Regs.TZSEL.bit.DCBEVT1 = 1;

EPwm2Regs.TZSEL.bit.DCAEVT1 = 1;

EPwm2Regs.TZSEL.bit.DCBEVT1 = 1;

EPwm3Regs.TZSEL.bit.DCAEVT1 = 1;

EPwm3Regs.TZSEL.bit.DCBEVT1 = 1;

// What do we want the DCAEVT1 and DCBEVT1 events to do?

// DCAEVTx events can force EPWMxA

// DCBEVTx events can force EPWMxB

EPwm1Regs.TZCTL.bit.TZA = TZ_FORCE_LO; // EPWM1A will go low

EPwm1Regs.TZCTL.bit.TZB = TZ_FORCE_LO; // EPWM1B will go low

EPwm2Regs.TZCTL.bit.TZA = TZ_FORCE_LO; // EPWM2A will go low

EPwm2Regs.TZCTL.bit.TZB = TZ_FORCE_LO; // EPWM2B will go low

EPwm3Regs.TZCTL.bit.TZA = TZ_FORCE_LO; // EPWM3A will go low

EPwm3Regs.TZCTL.bit.TZB = TZ_FORCE_LO; // EPWM3B will go low