Part Number: TMS320F28388D

大家好,

我在使用IPC进行CM4到CPU1通信时遇到一些问题,我使用下面帖子回答的用例进行修改

原代码内容:

//#############################################################################

//

// FILE: ipc_ex2_msgqueue_cm.c

//

// TITLE: IPC example with interrupt and message queue

//

//! \addtogroup driver_cm_c28x_dual_example_list

//! <h1> IPC message passing example with interrupt and message queue </h1>

//!

//! This example demonstrates how to configure IPC and pass information from

//! C28x to CM core with message queues.

//! It is recommended to run the C28x1 core first, followed by the CM core.

//!

//! \b External \b Connections \n

//! - None.

//!

//! \b Watch \b Variables \n

//! - None.

//!

//

//#############################################################################

// $Copyright:

// Copyright (C) 2022 Texas Instruments Incorporated - http://www.ti.com

//

// Redistribution and use in source and binary forms, with or without

// modification, are permitted provided that the following conditions

// are met:

//

// Redistributions of source code must retain the above copyright

// notice, this list of conditions and the following disclaimer.

//

// Redistributions in binary form must reproduce the above copyright

// notice, this list of conditions and the following disclaimer in the

// documentation and/or other materials provided with the

// distribution.

//

// Neither the name of Texas Instruments Incorporated nor the names of

// its contributors may be used to endorse or promote products derived

// from this software without specific prior written permission.

//

// THIS SOFTWARE IS PROVIDED BY THE COPYRIGHT HOLDERS AND CONTRIBUTORS

// "AS IS" AND ANY EXPRESS OR IMPLIED WARRANTIES, INCLUDING, BUT NOT

// LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR

// A PARTICULAR PURPOSE ARE DISCLAIMED. IN NO EVENT SHALL THE COPYRIGHT

// OWNER OR CONTRIBUTORS BE LIABLE FOR ANY DIRECT, INDIRECT, INCIDENTAL,

// SPECIAL, EXEMPLARY, OR CONSEQUENTIAL DAMAGES (INCLUDING, BUT NOT

// LIMITED TO, PROCUREMENT OF SUBSTITUTE GOODS OR SERVICES; LOSS OF USE,

// DATA, OR PROFITS; OR BUSINESS INTERRUPTION) HOWEVER CAUSED AND ON ANY

// THEORY OF LIABILITY, WHETHER IN CONTRACT, STRICT LIABILITY, OR TORT

// (INCLUDING NEGLIGENCE OR OTHERWISE) ARISING IN ANY WAY OUT OF THE USE

// OF THIS SOFTWARE, EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGE.

// $

//###########################################################################

//

// Included Files

//

#include "cm.h"

#include "ipc.h"

//

// Defines

//

#define IPC_CMD_READ_MEM 0x1001

#define IPC_CMD_RESP 0x2001

#define TEST_PASS 0x5555

#define TEST_FAIL 0xAAAA

IPC_MessageQueue_t messageQueue;

#pragma DATA_SECTION(CMData, "MSGRAM_CM_TO_CPU1")

uint32_t CMData[10];

//

// IPC ISR for Flag 1

// C28x core sends data with message queue using Flag 0

//

__interrupt void IPC_ISR1()

{

int i;

IPC_Message_t TxMsg, RxMsg;

bool status = false;

//

// Read the message from the message queue

//

IPC_readMessageFromQueue(IPC_CM_L_CPU1_R, &messageQueue, IPC_ADDR_CORRECTION_ENABLE,

&RxMsg, IPC_NONBLOCKING_CALL);

if(RxMsg.command == IPC_CMD_READ_MEM)

{

status = true;

//

// Read and compare data

//

for(i=0; i<RxMsg.dataw1; i++)

{

if((*(uint32_t *)RxMsg.address + i) != i)

status = false;

}

}

//

// Send response message

//

TxMsg.command = IPC_CMD_RESP;

TxMsg.address = (uint32_t)CMData;

TxMsg.dataw1 = 10;

TxMsg.dataw2 = 1;

IPC_sendMessageToQueue(IPC_CM_L_CPU1_R, &messageQueue, IPC_ADDR_CORRECTION_ENABLE,

&TxMsg, IPC_NONBLOCKING_CALL);

//

// Acknowledge the flag

//

IPC_ackFlagRtoL(IPC_CM_L_CPU1_R, IPC_FLAG1);

}

//

// Main

//

void main(void)

{

//

// Initialize device clock and peripherals

//

CM_init();

//

// Clear any IPC flags if set already

//

IPC_clearFlagLtoR(IPC_CM_L_CPU1_R, IPC_FLAG_ALL);

//

// Enable IPC interrupts

//

IPC_registerInterrupt(IPC_CM_L_CPU1_R, IPC_INT1, IPC_ISR1);

//

// Initialize message queue

//

IPC_initMessageQueue(IPC_CM_L_CPU1_R, &messageQueue, IPC_INT1, IPC_INT1);

//

// Synchronize both the cores.

//

IPC_sync(IPC_CM_L_CPU1_R, IPC_FLAG31);

int i;

for(i=0; i<10; i++)

{

CMData[i] = i+11;

}

//

// Loop forever. Wait for IPC interrupt

//

while(1);

}

//

// End of File

//

//#############################################################################

//

// FILE: ipc_ex2_msgqueue_c28x1.c

//

// TITLE: IPC example with interrupt and message queue

//

//! \addtogroup driver_cm_c28x_dual_example_list

//! <h1> IPC message passing example with interrupt and message queue </h1>

//!

//! This example demonstrates how to configure IPC and pass information from

//! C28x to CM core with message queues.

//! It is recommended to run the C28x1 core first, followed by the CM core.

//!

//! \b External \b Connections \n

//! - None.

//!

//! \b Watch \b Variables \n

//! - pass

//!

//

//#############################################################################

// $Copyright:

// Copyright (C) 2022 Texas Instruments Incorporated - http://www.ti.com

//

// Redistribution and use in source and binary forms, with or without

// modification, are permitted provided that the following conditions

// are met:

//

// Redistributions of source code must retain the above copyright

// notice, this list of conditions and the following disclaimer.

//

// Redistributions in binary form must reproduce the above copyright

// notice, this list of conditions and the following disclaimer in the

// documentation and/or other materials provided with the

// distribution.

//

// Neither the name of Texas Instruments Incorporated nor the names of

// its contributors may be used to endorse or promote products derived

// from this software without specific prior written permission.

//

// THIS SOFTWARE IS PROVIDED BY THE COPYRIGHT HOLDERS AND CONTRIBUTORS

// "AS IS" AND ANY EXPRESS OR IMPLIED WARRANTIES, INCLUDING, BUT NOT

// LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR

// A PARTICULAR PURPOSE ARE DISCLAIMED. IN NO EVENT SHALL THE COPYRIGHT

// OWNER OR CONTRIBUTORS BE LIABLE FOR ANY DIRECT, INDIRECT, INCIDENTAL,

// SPECIAL, EXEMPLARY, OR CONSEQUENTIAL DAMAGES (INCLUDING, BUT NOT

// LIMITED TO, PROCUREMENT OF SUBSTITUTE GOODS OR SERVICES; LOSS OF USE,

// DATA, OR PROFITS; OR BUSINESS INTERRUPTION) HOWEVER CAUSED AND ON ANY

// THEORY OF LIABILITY, WHETHER IN CONTRACT, STRICT LIABILITY, OR TORT

// (INCLUDING NEGLIGENCE OR OTHERWISE) ARISING IN ANY WAY OUT OF THE USE

// OF THIS SOFTWARE, EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGE.

// $

//###########################################################################

//

// Included Files

//

#include "driverlib.h"

#include "device.h"

//

// Defines

//

#define IPC_CMD_READ_MEM 0x1001

#define IPC_CMD_RESP 0x2001

#define TEST_PASS 0x5555

#define TEST_FAIL 0xAAAA

#pragma DATA_SECTION(CPU1Data, "MSGRAM_CPU_TO_CM")

uint32_t CPU1Data[10];

IPC_MessageQueue_t messageQueue;

IPC_Message_t TxMsg, RxMsg;

uint32_t pass;

__interrupt void IPC_ISR1()

{

int i;

bool status = false;

//

// Read the message from the message queue

//

IPC_readMessageFromQueue(IPC_CPU1_L_CM_R, &messageQueue, IPC_ADDR_CORRECTION_ENABLE,

&RxMsg, IPC_NONBLOCKING_CALL);

if(RxMsg.command == IPC_CMD_RESP)

{

status = true;

for(i=0; i<RxMsg.dataw1; i++)

{

if((*(uint32_t *)RxMsg.address + i) != i+11)

status = false;

}

}

//

// Send response message

//

TxMsg.command = IPC_CMD_READ_MEM;

TxMsg.address = (uint32_t)CPU1Data;

TxMsg.dataw1 = 10; // Using dataw1 as data length

TxMsg.dataw2 = 1; // Message identifier

IPC_sendMessageToQueue(IPC_CPU1_L_CM_R, &messageQueue, IPC_ADDR_CORRECTION_ENABLE,

&TxMsg, IPC_NONBLOCKING_CALL);

//

// Acknowledge the flag

//

IPC_ackFlagRtoL(IPC_CPU1_L_CM_R, IPC_FLAG1);

Interrupt_clearACKGroup(INTERRUPT_ACK_GROUP11);

}

//

// Main

//

void main(void)

{

int i;

//

// Initialize device clock and peripherals

//

Device_init();

//

// Boot CM core

//

#ifdef _FLASH

Device_bootCM(BOOTMODE_BOOT_TO_FLASH_SECTOR0);

#else

Device_bootCM(BOOTMODE_BOOT_TO_S0RAM);

#endif

//

// Initialize PIE and clear PIE registers. Disables CPU interrupts.

//

Interrupt_initModule();

//

// Initialize the PIE vector table with pointers to the shell Interrupt

// Service Routines (ISR).

//

Interrupt_initVectorTable();

//

// Clear any IPC flags if set already

//

IPC_clearFlagLtoR(IPC_CPU1_L_CM_R, IPC_FLAG_ALL);

//

// Enable IPC interrupts

//

IPC_registerInterrupt(IPC_CPU1_L_CM_R, IPC_INT1, IPC_ISR1);

//

// Initialize message queue

//

IPC_initMessageQueue(IPC_CPU1_L_CM_R, &messageQueue, IPC_INT1, IPC_INT1);

//

// Synchronize both the cores

//

IPC_sync(IPC_CPU1_L_CM_R, IPC_FLAG31);

//

// Enable Global Interrupt (INTM) and realtime interrupt (DBGM)

//

EINT;

ERTM;

//

// Fill in the data to be sent

//

for(i=0; i<10; i++)

{

CPU1Data[i] = i;

}

//

// Update the message

//

TxMsg.command = IPC_CMD_READ_MEM;

TxMsg.address = (uint32_t)CPU1Data;

TxMsg.dataw1 = 10; // Using dataw1 as data length

TxMsg.dataw2 = 1; // Message identifier

//

// Send message to the queue

// Since C28x and CM does not share the same address space for shared RAM,

// ADDRESS_CORRECTION is enabled

//

IPC_sendMessageToQueue(IPC_CPU1_L_CM_R, &messageQueue, IPC_ADDR_CORRECTION_ENABLE,

&TxMsg, IPC_NONBLOCKING_CALL);

//

// End of example. Loop forever

//

while(1);

}

//

// End of File

//

修改内容:

1、我在CM4核的while循环上不断发送消息至CPU1,发现CPU1无法重复进入中断,请问是什么原因造成的?

ipc_ex2_msgqueue_cm.c

//

// End of example. Loop forever

//

while(1)

{

//

// Send response message

//

TxMsg.command = IPC_CMD_RESP;

TxMsg.address = (uint32_t)CMData;

TxMsg.dataw1 = 10;

TxMsg.dataw2 = 1;

IPC_sendMessageToQueue(IPC_CM_L_CPU1_R, &messageQueue, IPC_ADDR_CORRECTION_ENABLE,

&TxMsg, IPC_NONBLOCKING_CALL);

}

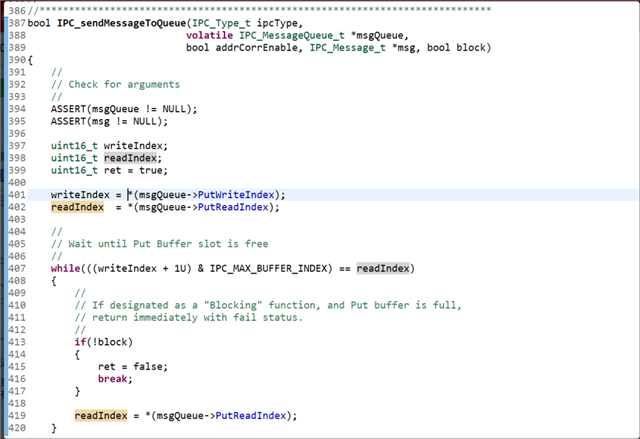

2、想问下消息队列的阻塞方式和非阻塞方式该如何理解?