请问这个问题有什么解释吗?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

void Init_EPWM()

{

EALLOW;

SysCtrlRegs.PCLKCR0.bit.TBCLKSYNC = 0; // Disable TBCLK within the EPWM

EDIS;

Init_epwm1();

Init_epwm2();

// Init_epwm3();

EALLOW;

SysCtrlRegs.PCLKCR0.bit.TBCLKSYNC = 1; // Enable TBCLK within the EPWM

EDIS;

}

//=======================================================

//函数名称: Init_epwm1()

//功能: 初始化EPWM1为带死区互补输出(AHC)的可变频率的PWM 逆变级

//输入:

//返回:

//备注:

//=======================================================

void Init_epwm1(void)

{

EPwm1Regs.TBCTL.bit.CTRMODE = TB_COUNT_UPDOWN; // Count up-down

EPwm1Regs.TBCTL.bit.HSPCLKDIV = TB_DIV1; // TBCLK = EPWMCLK /(HSPCLKDIV× CLKDIV)

EPwm1Regs.TBCTL.bit.CLKDIV = TB_DIV1; // TBCLK = 150M/(1*1)= 150MHz

EPwm1Regs.TBCTL.bit.PHSEN = TB_DISABLE; // Enable phase loading

EPwm1Regs.TBCTL.bit.PRDLD = TB_SHADOW; // TBPRD is loaded from its shadow register

EPwm1Regs.TBPRD = EPWM_PRD; // Set timer period (100kHz)

EPwm1Regs.TBPHS.half.TBPHS = 0x0000; // Phase is 0

EPwm1Regs.TBCTR = 0x0000; // Clear counter

EPwm1Regs.TBCTL.bit.SYNCOSEL = TB_CTR_ZERO; // 同步信号输出选择TBCTR=0

EPwm1Regs.CMPCTL.bit.SHDWAMODE = CC_SHADOW; // CMPA Shadow mode

EPwm1Regs.CMPCTL.bit.LOADAMODE = CC_CTR_ZERO; // Load on CTR = 0

EPwm1Regs.CMPCTL.bit.SHDWBMODE = CC_SHADOW; // CMPA Shadow mode

EPwm1Regs.CMPCTL.bit.LOADBMODE = CC_CTR_ZERO; // Load on CTR = 0

EPwm1Regs.CMPA.half.CMPA = 2*D* EPWM_PRD; // Initial duty

EPwm1Regs.AQCTLA.bit.CAU = AQ_CLEAR; // TBCTR = CMPA on Down Count:Clear

EPwm1Regs.AQCTLA.bit.CAD = AQ_NO_ACTION; // TBCTR = CMPA on Up Count:NO ACTION

EPwm1Regs.AQCTLA.bit.ZRO = AQ_SET; // TBCTR = 0 on Up Count:Set

// EPwm1Regs.AQCTLB.bit.CAU = AQ_CLEAR; // TBCTR = CMPA on Down Count:Clear

// EPwm1Regs.AQCTLB.bit.CAD = AQ_NO_ACTION; // TBCTR = CMPA on Up Count:NO ACTION

// EPwm1Regs.AQCTLB.bit.ZRO = AQ_SET; // T BCTR = 0 on Up Count:Set

EPwm1Regs.AQCTLB.bit.CAU = AQ_NO_ACTION;

EPwm1Regs.AQCTLB.bit.CAD = AQ_CLEAR;

EPwm1Regs.AQCTLB.bit.ZRO = AQ_SET;

//DELAY_US(100000);

EPwm1Regs.DBCTL.bit.OUT_MODE = DB_FULL_ENABLE; //0x3 MODE2 AHC high level delay (AHC)死区双边使能

EPwm1Regs.DBCTL.bit.POLSEL = DB_ACTV_HIC; //0x2 A不反转,B反转

EPwm1Regs.DBCTL.bit.IN_MODE = DBA_RED_DBB_FED;

EPwm1Regs.DBRED = EPWM1_DBRED; // 上升沿延时 注意:只有10位,最大1023

EPwm1Regs.DBFED = EPWM1_DBFED; // 下降沿延时 注意:只有10位,最大1023

EALLOW;

EPwm1Regs.TZSEL.bit.OSHT1 = 1; //单次触发联防

// EPwm1Regs.TZSEL.bit.OSHT2 = 1; //单次触发联防

EPwm1Regs.TZCTL.bit.TZA = TZ_FORCE_LO; //强制A低电平

EPwm1Regs.TZCTL.bit.TZB = TZ_FORCE_LO; //强制B低电平

//

// // Enable TZ interrupt

//

EPwm1Regs.TZEINT.bit.OST = 1;

EDIS;

//

EALLOW;

EPwm1Regs.ETSEL.bit.INTSEL = ET_CTR_ZERO; //过零点触发中断

EPwm1Regs.ETSEL.bit.INTEN = 1; //使能中断

EPwm1Regs.ETPS.bit.INTPRD = ET_1ST; //每次过零产生中断

EDIS;

//计数器计数等于0时触发ADC转换

// EPwm1Regs.ETSEL.bit.SOCASEL = ET_CTR_ZERO; // Counter = 0

// EPwm1Regs.ETPS.bit.SOCAPRD = ET_1ST; // Generate SOCA pulse on 1st event

// EPwm1Regs.ETCLR.bit.SOCA = 1; // Clear SOCA flag

// EPwm1Regs.ETSEL.bit.SOCAEN = 1; // Enable SOCA

// EPwm1Regs.ETCLR.bit.INT = 1; // Clear INT flag

// EPwm1Regs.ETSEL.bit.INTEN = 0; // Disable INT

}

void Init_epwm2(void)

{

EPwm2Regs.TBCTL.bit.CTRMODE = TB_COUNT_UPDOWN; // Count up-down

EPwm2Regs.TBCTL.bit.HSPCLKDIV = TB_DIV1; // TBCLK = EPWMCLK /(HSPCLKDIV× CLKDIV)

EPwm2Regs.TBCTL.bit.CLKDIV = TB_DIV1; // TBCLK = 150M/(1*1)= 150MHz

EPwm2Regs.TBCTL.bit.PHSEN = TB_ENABLE; // Enable phase loading

EPwm2Regs.TBCTL.bit.PRDLD = TB_SHADOW; // TBPRD is loaded from its shadow register

EPwm2Regs.TBPRD = EPWM_PRD; // Set timer period (4.8kHz)

EPwm2Regs.TBPHS.half.TBPHS = 0;

EPwm2Regs.TBCTR = 0x0000; // Clear counter

EPwm2Regs.TBCTL.bit.SYNCOSEL = TB_SYNC_IN; // 同步信号输出选择外部同步信号输入EPWMxSYNCO

EPwm2Regs.CMPCTL.bit.SHDWAMODE = CC_SHADOW; // CMPA Shadow mode

EPwm2Regs.CMPCTL.bit.LOADAMODE = CC_CTR_ZERO; // Load on CTR = 0

EPwm2Regs.CMPCTL.bit.SHDWBMODE = CC_SHADOW; // CMPA Shadow mode

EPwm2Regs.CMPCTL.bit.LOADBMODE = CC_CTR_ZERO; // Load on CTR = 0

EPwm2Regs.CMPA.half.CMPA = 2*D* EPWM_PRD; // Initial duty

// EPwm2Regs.AQCTLA.bit.CAU = AQ_CLEAR; // TBCTR = CMPA on Down Count:Clear

// EPwm2Regs.AQCTLA.bit.CAD = AQ_NO_ACTION; // TBCTR = CMPA on Up Count:NO ACTION

// EPwm2Regs.AQCTLA.bit.ZRO = AQ_SET; // TBCTR = 0 on Up Count:Set

//

// EPwm2Regs.AQCTLB.bit.CAU = AQ_NO_ACTION;

// EPwm2Regs.AQCTLB.bit.CAD = AQ_CLEAR;

// EPwm2Regs.AQCTLB.bit.ZRO = AQ_SET;

//

// EPwm2Regs.DBCTL.bit.OUT_MODE = DB_FULL_ENABLE; //0x3 MODE2 AHC high level delay (AHC)死区双边使能

// EPwm2Regs.DBCTL.bit.POLSEL = DB_ACTV_HIC; //0x1 A不反转,B反转

// EPwm2Regs.DBCTL.bit.IN_MODE = DBA_RED_DBB_FED;

// EPwm2Regs.AQCTLA.bit.CAU = AQ_NO_ACTION; // TBCTR = CMPA on Down Count:Clear

// EPwm2Regs.AQCTLA.bit.CAD = AQ_SET; // TBCTR = CMPA on Up Count:Set

// EPwm2Regs.AQCTLA.bit.ZRO = AQ_CLEAR;

//

// EPwm2Regs.AQCTLB.bit.CAU = AQ_SET;

// EPwm2Regs.AQCTLB.bit.CAD = AQ_NO_ACTION;

// EPwm2Regs.AQCTLB.bit.ZRO = AQ_CLEAR;

EPwm2Regs.AQCTLA.bit.CAU = AQ_CLEAR; // TBCTR = CMPA on Down Count:Clear

EPwm2Regs.AQCTLA.bit.CAD = AQ_NO_ACTION; // TBCTR = CMPA on Up Count:NO ACTION

EPwm2Regs.AQCTLA.bit.ZRO = AQ_SET; // TBCTR = 0 on Up Count:Set

// EPwm2Regs.AQCTLA.bit.CAU = AQ_CLEAR; // TBCTR = CMPA on Down Count:Clear

// EPwm2Regs.AQCTLA.bit.CAD = AQ_NO_ACTION; // TBCTR = CMPA on Up Count:NO ACTION

// EPwm2Regs.AQCTLA.bit.ZRO = AQ_NO_ACTION; // TBCTR = 0 on Up Count:Set

//

// EPwm2Regs.AQCTLB.bit.CAU = AQ_CLEAR;

// EPwm2Regs.AQCTLB.bit.CAD = AQ_NO_ACTION;

// EPwm2Regs.AQCTLB.bit.ZRO = AQ_NO_ACTION;

EPwm2Regs.AQCTLB.bit.CAU = AQ_NO_ACTION;

EPwm2Regs.AQCTLB.bit.CAD = AQ_CLEAR;

EPwm2Regs.AQCTLB.bit.ZRO = AQ_SET;

EPwm2Regs.DBCTL.bit.OUT_MODE = DB_FULL_ENABLE; //0x3 MODE2 AHC high level delay (AHC)死区双边使能

EPwm2Regs.DBCTL.bit.POLSEL = DB_ACTV_HIC; //0x2 A不反转,B反转

// EPwm2Regs.DBCTL.bit.POLSEL = DB_ACTV_HI; //0x2 A不反转,B不反转

EPwm2Regs.DBCTL.bit.IN_MODE = DBA_RED_DBB_FED;

// EPwm2Regs.DBCTL.bit.OUT_MODE = DB_FULL_ENABLE; //0x3 MODE2 AHC high level delay (AHC)死区双边使能

// EPwm2Regs.DBCTL.bit.POLSEL = DB_ACTV_HIC; //0x2

// EPwm2Regs.DBCTL.bit.IN_MODE = DBA_RED_DBB_FED;

EPwm2Regs.DBRED = EPWM2_DBRED; // 上升沿延时 上升死区为0.5%的占空比 0.5%个TBPRD(150MHz) 注意:只有10位,最大1023

EPwm2Regs.DBFED = EPWM2_DBFED; // 下降沿延时 下降死区为0.5%的占空比 0.5%个TBPRD(150MHz) 注意:只有10位,最大1023

EALLOW;

EPwm2Regs.TZSEL.bit.OSHT1 = 1;

EPwm2Regs.TZCTL.bit.TZA = TZ_FORCE_LO;

EPwm2Regs.TZCTL.bit.TZB = TZ_FORCE_LO;

//Enable TZ interrupt

// EPwm2Regs.TZEINT.bit.CBC =1;

EPwm2Regs.TZEINT.bit.OST = 1;

EDIS;

// EALLOW;

// //EPwm1Regs.AQCSFRC.all=0x05; //强制低

// EPwm2Regs.AQCSFRC.all=0x05; //强制低

// // EPwm3Regs.AQCSFRC.all=0x05;

// // EPwm6Regs.AQCSFRC.all=0x05;

// EPwm2Regs.DBCTL.bit.POLSEL = 0x0; //不反转极性

// EDIS;

}

如图上代码所示,Init_EPWM()为PWM初始化函数,其流程是先关闭TBCLKSYNC时基时钟,再进行配置,配置结束后再开启时基时钟。另外你说的外设时钟,不知道是不是这片代码。这片代码在工程文件的DSP2833x_SysCtrl.c源文件里,并未改动。

SysCtrlRegs.PCLKCR0.bit.TBCLKSYNC = 0; // Disable TBCLK within the ePWM

SysCtrlRegs.PCLKCR1.bit.EPWM1ENCLK = 1; // ePWM1

SysCtrlRegs.PCLKCR1.bit.EPWM2ENCLK = 1; // ePWM2

SysCtrlRegs.PCLKCR1.bit.EPWM3ENCLK = 1; // ePWM3

SysCtrlRegs.PCLKCR1.bit.EPWM4ENCLK = 1; // ePWM4

SysCtrlRegs.PCLKCR1.bit.EPWM5ENCLK = 1; // ePWM5

SysCtrlRegs.PCLKCR1.bit.EPWM6ENCLK = 1; // ePWM6

SysCtrlRegs.PCLKCR0.bit.TBCLKSYNC = 1; // Enable TBCLK within the ePWM

2.配置完后清除了TBCLR计数器,还是有这个现象。

3,这个现象出现在在翻转的那一路PWM上,不论PWM动作模块怎么配置,只要在死区模块中把该路PWM翻转,PWM输出不论输出高电平,还是低电平,第一个脉冲时钟就有一段高电平。这段高电平过后就是正常的PWM波。这个现象也出现在直接购买的28335开发板上。

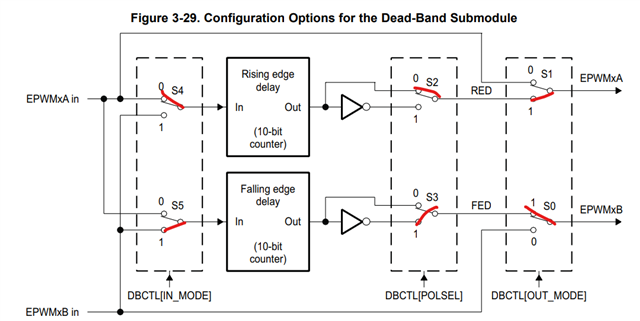

为了方便之后查看,我把DB的配置发上来:

另外为了方便查看,我把你之前上传的代码的格式改了一下

关键配置:

EPwm1Regs.TBCTL.bit.CTRMODE = TB_COUNT_UPDOWN; EPwm1Regs.TBCTR = 0x0000; EPwm1Regs.CMPA.half.CMPA = 2 * D * EPWM_PRD; EPwm1Regs.AQCTLA.bit.CAU = AQ_CLEAR; EPwm1Regs.AQCTLA.bit.ZRO = AQ_SET; EPwm1Regs.AQCTLB.bit.CAD = AQ_CLEAR; EPwm1Regs.AQCTLB.bit.ZRO = AQ_SET; EPwm1Regs.DBCTL.bit.OUT_MODE = DB_FULL_ENABLE; EPwm1Regs.DBCTL.bit.POLSEL = DB_ACTV_HIC; //B reverse EPwm1Regs.DBCTL.bit.IN_MODE = DBA_RED_DBB_FED; EPwm1Regs.DBRED = EPWM1_DBRED; EPwm1Regs.DBFED = EPWM1_DBFED;

实验结果:

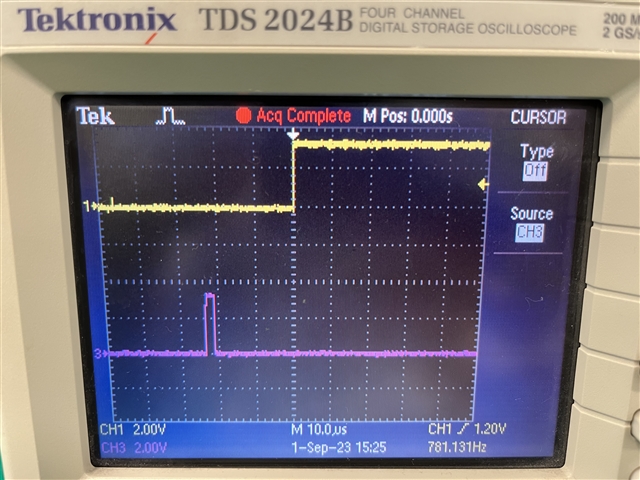

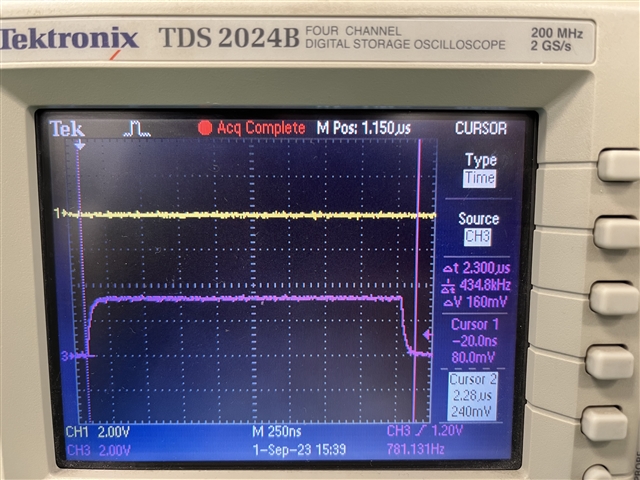

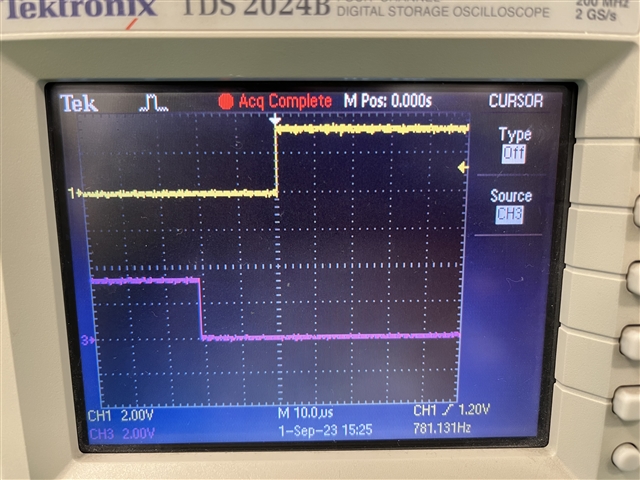

第1、第2个波形分别是第一个PWM波之前的高电平脉冲以及它的宽度;

第3个波形是之后的PWM波。

黄色的是1A,紫色的是1B。

不难看出,1B脉冲的下降沿 到 1A的上升沿 之间是设定的1A的上升沿延迟。

根据实验推断的原因是DB模块中存在延时。

1B的配置是0处置1,CAD处清0;但是加入了翻转,也就是说实际上是在CAD附近置1,紧接着在0处清0。

上面提到的DB模块中的延时为低电平,是在第一个0处清零(翻转前是置高)之前,被翻转了上去,所以产生了脉冲。