Other Parts Discussed in Thread: C2000WARE

专家你好,我使用CCS配置CLA,生成后套用C盘软件安装目录里C2000Ware_5_00_00_00里的cla_ex1_asin模板。asin

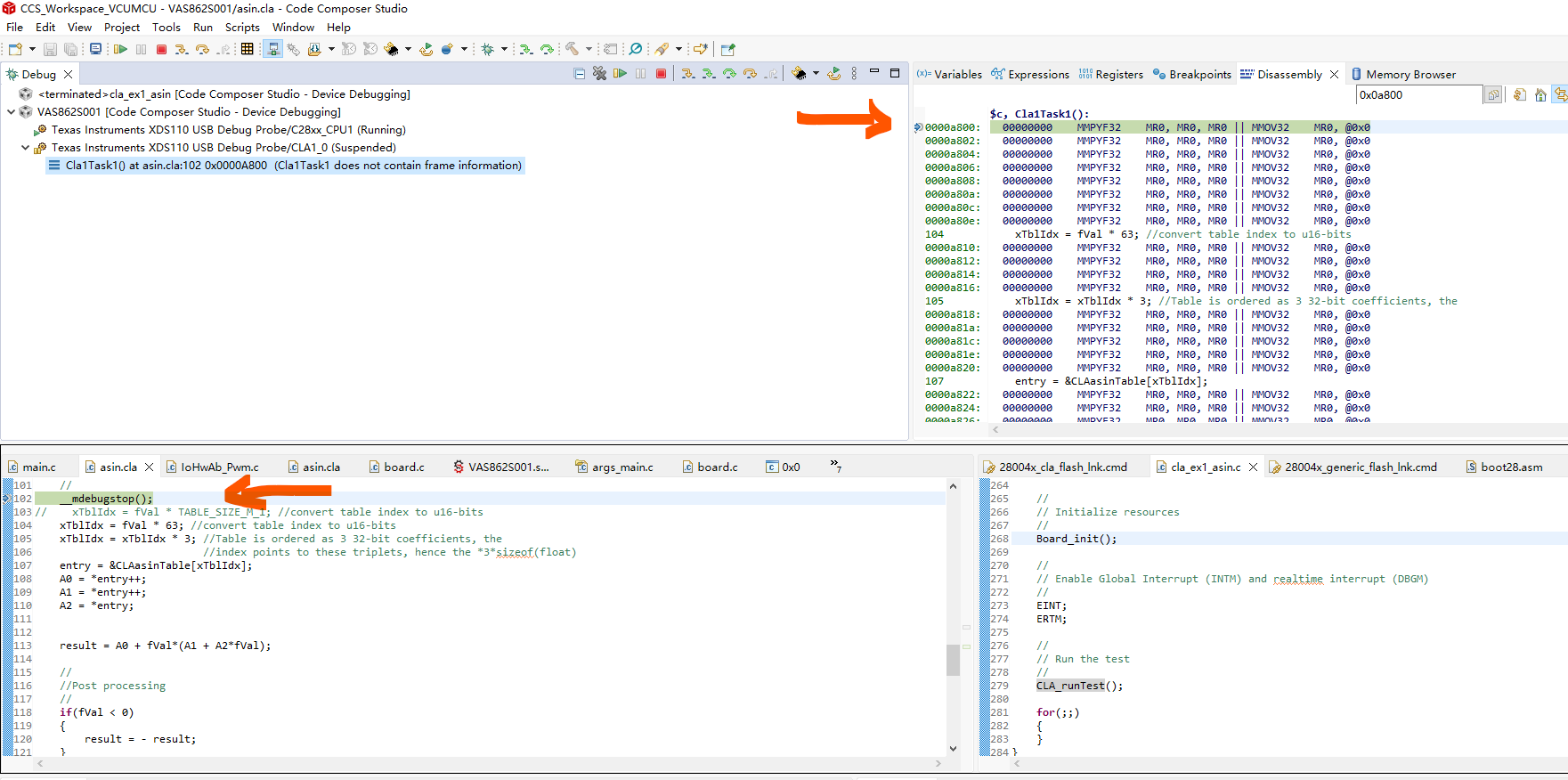

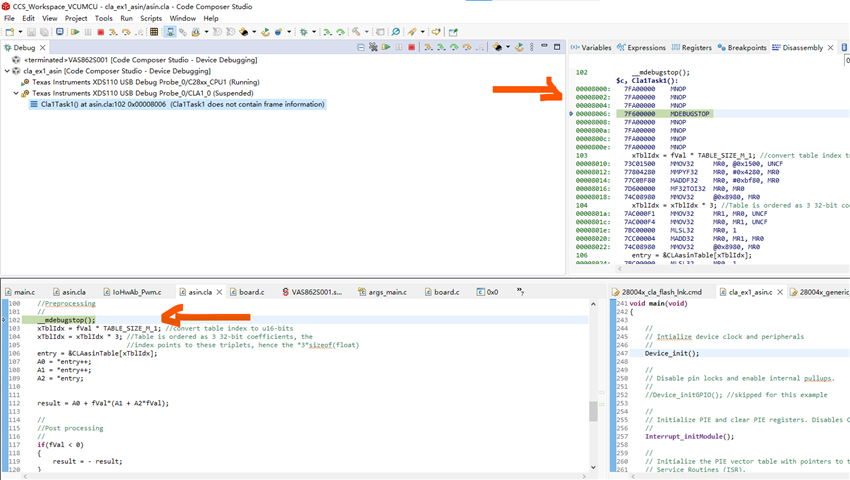

使用模板能够正常调试CLA,也能在CLA里单步调试,能正常使用。

但是将模板的主要代码asin.cla、cla_ex1_asin_shared.h,还有其他代码移植到我的工程后无法正常调试和使用CLA。

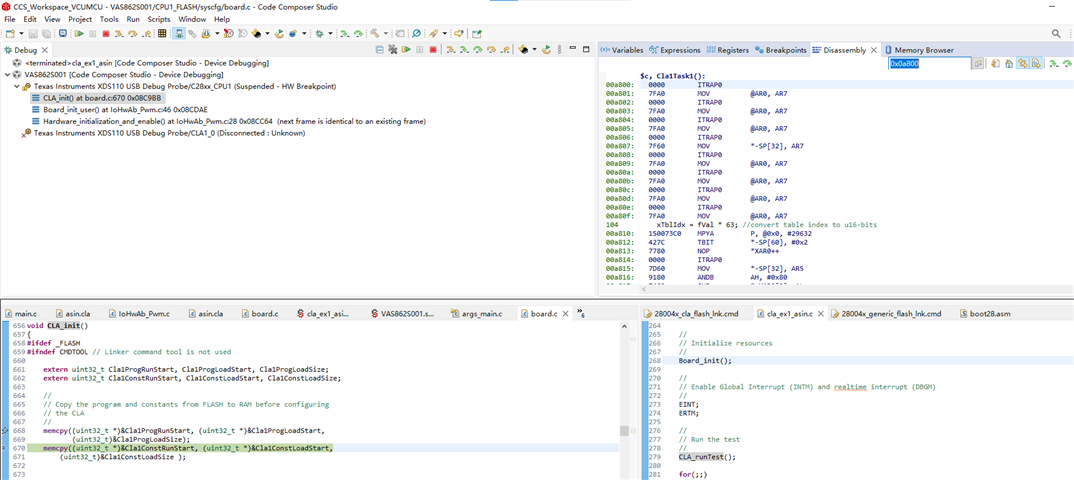

具体现象如下:1.Cla1ProgRunStart能够将CLA程序从Flash拷贝到RAMLS0,memory中有显示相关代码。

2.在DEBUG界面CLA,Load Symbols后显示no symbols are defined

3.运行CLA_runTest()时y数组没有变化,y数值依然是初始值0。

board.c部分相关代码如下:

#include "board.h"

//*****************************************************************************

//

// Board Configurations

// Initializes the rest of the modules.

// Call this function in your application if you wish to do all module

// initialization.

// If you wish to not use some of the initializations, instead of the

// Board_init use the individual Module_inits

//

//*****************************************************************************

void Board_init()

{

EALLOW;

PinMux_init();

SYNC_init();

ASYSCTL_init();

CLA_init();

MEMCFG_init();

ADC_init();

AIO_init();

CPUTIMER_init();

EPWM_init();

GPIO_init();

PGA_init();

INTERRUPT_init();

EDIS;

}

//*****************************************************************************

//

// CLA Configurations

//

//*****************************************************************************

void myCLA0_init(){

//

// Configure all CLA task vectors

// On Type-1 and Type-2 CLAs the MVECT registers accept full 16-bit task addresses as

// opposed to offsets used on older Type-0 CLAs

//

#pragma diag_suppress=770

//

// CLA Task 1

//

CLA_mapTaskVector(myCLA0_BASE, CLA_MVECT_1, (uint16_t)&Cla1Task1);

CLA_setTriggerSource(CLA_TASK_1, CLA_TRIGGER_SOFTWARE);

//

// CLA Task 2

//

CLA_mapTaskVector(myCLA0_BASE, CLA_MVECT_2, (uint16_t)&Cla1Task2);

CLA_setTriggerSource(CLA_TASK_2, CLA_TRIGGER_SOFTWARE);

//

// CLA Task 3

//

CLA_mapTaskVector(myCLA0_BASE, CLA_MVECT_3, (uint16_t)&Cla1Task3);

CLA_setTriggerSource(CLA_TASK_3, CLA_TRIGGER_SOFTWARE);

//

// CLA Task 4

//

CLA_mapTaskVector(myCLA0_BASE, CLA_MVECT_4, (uint16_t)&Cla1Task4);

CLA_setTriggerSource(CLA_TASK_4, CLA_TRIGGER_SOFTWARE);

//

// CLA Task 5

//

CLA_mapTaskVector(myCLA0_BASE, CLA_MVECT_5, (uint16_t)&Cla1Task5);

CLA_setTriggerSource(CLA_TASK_5, CLA_TRIGGER_SOFTWARE);

//

// CLA Task 6

//

CLA_mapTaskVector(myCLA0_BASE, CLA_MVECT_6, (uint16_t)&Cla1Task6);

CLA_setTriggerSource(CLA_TASK_6, CLA_TRIGGER_SOFTWARE);

//

// CLA Task 7

//

CLA_mapTaskVector(myCLA0_BASE, CLA_MVECT_7, (uint16_t)&Cla1Task7);

CLA_setTriggerSource(CLA_TASK_7, CLA_TRIGGER_SOFTWARE);

//

// CLA Task 8

//

CLA_mapTaskVector(myCLA0_BASE, CLA_MVECT_8, (uint16_t)&Cla1Task8);

CLA_setTriggerSource(CLA_TASK_8, CLA_TRIGGER_SOFTWARE);

//

// Disable background task

//

CLA_disableBackgroundTask(myCLA0_BASE);

#pragma diag_warning=770

//

// Enable the IACK instruction to start a task on CLA in software

// for all 8 CLA tasks. Also, globally enable all 8 tasks (or a

// subset of tasks) by writing to their respective bits in the

// MIER register

//

CLA_enableIACK(myCLA0_BASE);

CLA_enableTasks(myCLA0_BASE, CLA_TASKFLAG_ALL);

}

void CLA_init()

{

#ifdef _FLASH

#ifndef CMDTOOL // Linker command tool is not used

extern uint32_t Cla1ProgRunStart, Cla1ProgLoadStart, Cla1ProgLoadSize;

extern uint32_t Cla1ConstRunStart, Cla1ConstLoadStart, Cla1ConstLoadSize;

//

// Copy the program and constants from FLASH to RAM before configuring

// the CLA

//

memcpy((uint32_t *)&Cla1ProgRunStart, (uint32_t *)&Cla1ProgLoadStart,

(uint32_t)&Cla1ProgLoadSize);

memcpy((uint32_t *)&Cla1ConstRunStart, (uint32_t *)&Cla1ConstLoadStart,

(uint32_t)&Cla1ConstLoadSize );

#endif //CMDTOOL

#endif //_FLASH

myCLA0_init();

}

//*****************************************************************************

//

// INTERRUPT Configurations

//

//*****************************************************************************

void INTERRUPT_init(){

// Interrupt Setings for INT_myCLA01

Interrupt_register(INT_myCLA01, &cla1Isr1);

Interrupt_enable(INT_myCLA01);

// Interrupt Setings for INT_myCLA02

Interrupt_register(INT_myCLA02, &cla1Isr2);

Interrupt_enable(INT_myCLA02);

// Interrupt Setings for INT_myCLA03

Interrupt_register(INT_myCLA03, &cla1Isr3);

Interrupt_enable(INT_myCLA03);

// Interrupt Setings for INT_myCLA04

Interrupt_register(INT_myCLA04, &cla1Isr4);

Interrupt_enable(INT_myCLA04);

// Interrupt Setings for INT_myCLA05

Interrupt_register(INT_myCLA05, &cla1Isr5);

Interrupt_enable(INT_myCLA05);

// Interrupt Setings for INT_myCLA06

Interrupt_register(INT_myCLA06, &cla1Isr6);

Interrupt_enable(INT_myCLA06);

// Interrupt Setings for INT_myCLA07

Interrupt_register(INT_myCLA07, &cla1Isr7);

Interrupt_enable(INT_myCLA07);

// Interrupt Setings for INT_myCLA08

Interrupt_register(INT_myCLA08, &cla1Isr8);

Interrupt_enable(INT_myCLA08);

// Interrupt Setings for INT_timer2

Interrupt_register(INT_timer2, &portTICK_ISR);

Interrupt_disable(INT_timer2);

// Interrupt Setings for INT_myADCA_1

Interrupt_register(INT_myADCA_1, &adcA1ISR);

Interrupt_enable(INT_myADCA_1);

// Interrupt Setings for INT_myADCB_1

Interrupt_register(INT_myADCB_1, &INT_myADCB_1_ISR);

Interrupt_enable(INT_myADCB_1);

// Interrupt Setings for INT_myADCB_4

Interrupt_register(INT_myADCB_4, &INT_myADCB_4_ISR);

Interrupt_enable(INT_myADCB_4);

// Interrupt Setings for INT_myADCC_1

Interrupt_register(INT_myADCC_1, &INT_myADCC_1_ISR);

Interrupt_enable(INT_myADCC_1);

// Interrupt Setings for INT_myADCC_2

Interrupt_register(INT_myADCC_2, &INT_myADCC_2_ISR);

Interrupt_enable(INT_myADCC_2);

// Interrupt Setings for INT_myADCC_3

Interrupt_register(INT_myADCC_3, &INT_myADCC_3_ISR);

Interrupt_enable(INT_myADCC_3);

// Interrupt Setings for INT_myADCC_4

Interrupt_register(INT_myADCC_4, &INT_myADCC_4_ISR);

Interrupt_enable(INT_myADCC_4);

}

main.c代码如下:

//#############################################################################

//

//

//#############################################################################

//

// Included Files

//

#include "driverlib.h"

#include "board.h"

#include "device.h"

#include "clocktree.h"

#define MSGCOUNT 10000

const char gcs8_Software_Version[19] = {'V','A','S','8','6','2','S','0','0','1',0xFF,0xFF,0xFF,0xFF,0xFF,0xFF,0xFF,0xFF,0xFF};//VAS341C110;

const char gcs8_Hardware_Version[14] = {'V','A','1','0','5','1','-','0','0','1','T'};//VA1064A-002A;

const char gcs8_PCB_Version[12] = {'V','A','1','0','5','1','-','0','0','1','T'};//VA1060A-003A;

#include "cla_ex1_asin_shared.h"

//

// Defines

//

#define WAITSTEP asm(" RPT #255 || NOP")

//

// Globals

//

//

//Task 1 (C) Variables

// NOTE: Do not initialize the Message RAM variables globally, they will be

// reset during the message ram initialization phase in the CLA memory

// configuration routine

//

#ifdef __cplusplus

#pragma DATA_SECTION("CpuToCla1MsgRAM");

float fVal;

#pragma DATA_SECTION("Cla1ToCpuMsgRAM");

float fResult;

#else

#pragma DATA_SECTION(fVal,"CpuToCla1MsgRAM");

float fVal;

#pragma DATA_SECTION(fResult,"Cla1ToCpuMsgRAM");

float fResult;

#endif //__cplusplus

float y[BUFFER_SIZE];

//

//Task 2 (C) Variables

//

//

//Task 3 (C) Variables

//

//

//Task 4 (C) Variables

//

//

//Task 5 (C) Variables

//

//

//Task 6 (C) Variables

//

//

//Task 7 (C) Variables

//

//

//Task 8 (C) Variables

//

//

//Common (C) Variables

//The Exponential table

//

#ifdef __cplusplus

#pragma DATA_SECTION("CLADataLS1")

#else

#pragma DATA_SECTION(CLAasinTable,"CLADataLS1")

#endif //__cplusplus

float CLAasinTable[]={

0.0, 1.0, 0.0,

0.000000636202, 0.999877862610, 0.007815361896,

0.000005099694, 0.999510644409, 0.015647916155,

0.000017268312, 0.998895919094, 0.023514960332,

0.000041121765, 0.998029615282, 0.031434003631,

0.000080794520, 0.996905974725, 0.039422875916,

0.000140631089, 0.995517492804, 0.047499840611,

0.000225244584, 0.993854840311, 0.055683712914,

0.000339579512, 0.991906765146, 0.063993984848,

0.000488979852, 0.989659972212, 0.072450958820,

0.000679263611, 0.987098979366, 0.081075891529,

0.000916805182, 0.984205946802, 0.089891150305,

0.001208627040, 0.980960476685, 0.098920384204,

0.001562502549, 0.977339379243, 0.108188712551,

0.001987071928, 0.973316400729, 0.117722933997,

0.002491973784, 0.968861907789, 0.127551759665,

0.003087995053, 0.963942521723, 0.137706074532,

0.003787242692, 0.958520694794, 0.148219231941,

0.004603341138, 0.952554219267, 0.159127386977,

0.005551660294, 0.945995657913, 0.170469875522,

0.006649579796, 0.938791682505, 0.182289647088,

0.007916796475, 0.930882303984, 0.194633761132,

0.009375683410, 0.922199974574, 0.207553958472,

0.011051710808, 0.912668537890, 0.221107321885,

0.012973941175, 0.902201997769, 0.235357042896,

0.015175614174, 0.890703070035, 0.250373315541,

0.017694840102, 0.878061473098, 0.266234382514,

0.020575425537, 0.864151902887, 0.283027765009,

0.023867860513, 0.848831624374, 0.300851714968,

0.027630504055, 0.831937595031, 0.319816937941,

0.031931014547, 0.813283013821, 0.340048646894,

0.036848083955, 0.792653161200, 0.361689022958,

0.042473551274, 0.769800358920, 0.384900179460,

0.048914992206, 0.744437830278, 0.409867752228,

0.056298910750, 0.716232177740, 0.436805274317,

0.064774696786, 0.684794109766, 0.465959540059,

0.074519565699, 0.649666934178, 0.497617226179,

0.085744766889, 0.610312179660, 0.532113122767,

0.098703445606, 0.566091493186, 0.569840443472,

0.113700678529, 0.516243664372, 0.611263845480,

0.131106395009, 0.459855210927, 0.656936015611,

0.151372169232, 0.395822366759, 0.707518998893,

0.175053263659, 0.322801460177, 0.763811905770,

0.202837883870, 0.239143420888, 0.826787304376,

0.235586468765, 0.142806299514, 0.897639596948,

0.274385149825, 0.031236880585, 0.977850174820,

0.320619535938, -0.098791845166, 1.069276441800,

0.376078169620, -0.251407364538, 1.174275392129,

0.443100143614, -0.431959397725, 1.295878193174,

0.524789871827, -0.647485610469, 1.438041695773,

0.625336471263, -0.907400624736, 1.606018804842,

0.750500589935, -1.224540947101, 1.806917563896,

0.908377657341, -1.616794995066, 2.050569262035,

1.110633894185, -2.109729648039, 2.350920816737,

1.374584721437, -2.740985157716, 2.728353889708,

1.726848242753, -3.567962877198, 3.213722960014,

2.210117561056, -4.682006534082, 3.855770086891,

2.896554011854, -6.236312386687, 4.735651038017,

3.916505715382, -8.505488022524, 5.997790945975,

5.526855868703, -12.026617159136, 7.922628470498,

8.298197116322, -17.983705080358, 11.123941286820,

13.741706072449, -29.488929624542, 17.203344479111,

27.202707817485, -57.466598393615, 31.741016484669,

83.158101335898, -171.803399517566, 90.149831709374

};

float asin_expected[BUFFER_SIZE]={

1.570796, 1.393789, 1.320141, 1.263401, 1.215375,

1.172892, 1.134327, 1.098718, 1.065436, 1.034046,

1.004232, 0.9757544, 0.9484279, 0.9221048, 0.8966658,

0.8720123, 0.8480621, 0.8247454, 0.8020028, 0.7797828,

0.7580408, 0.7367374, 0.7158381, 0.6953120, 0.6751316,

0.6552721, 0.6357113, 0.6164289, 0.5974064, 0.5786270,

0.5600753, 0.5417370, 0.5235988, 0.5056486, 0.4878751,

0.4702678, 0.4528166, 0.4355124, 0.4183464, 0.4013104,

0.3843968, 0.3675981, 0.3509074, 0.3343180, 0.3178237,

0.3014185, 0.2850964, 0.2688521, 0.2526802, 0.2365756,

0.2205333, 0.2045484, 0.1886164, 0.1727327, 0.1568929,

0.1410927, 0.1253278, 0.1095943, 0.09388787, 0.07820469,

0.06254076, 0.04689218, 0.03125509, 0.01562564

};

uint16_t pass = 0;

uint16_t fail = 0;

//

// Function Prototypes

//

void CLA_runTest(void);

__interrupt void cla1Isr1();

__interrupt void cla1Isr2();

__interrupt void cla1Isr3();

__interrupt void cla1Isr4();

__interrupt void cla1Isr5();

__interrupt void cla1Isr6();

__interrupt void cla1Isr7();

__interrupt void cla1Isr8();

void main(void)

{

demo_mea();

Device_init();

Device_initGPIO();

Interrupt_initModule();

Interrupt_initVectorTable();

Can_Drv_Init();

Can_SetConfig();

Hardware_initialization_and_enable();

//

// Enable Global Interrupt (INTM) and realtime interrupt (DBGM)

//

EINT;

ERTM;

// Can_Test();

// Ccp_Init();

// EcuM_Init();

//

// Run the test

//

CLA_runTest();

for(;;)

{

}

// while(1)

// {

//

// }

//

// Stop application after completion.

//

asm(" ESTOP0");

}

//

// CLA_runTest - Execute CLA task tests for specified vectors

//

void CLA_runTest(void)

{

int16_t i;

float error;

for(i = 0; i < BUFFER_SIZE; i++)

{

fVal= (float)(BUFFER_SIZE - i)/(float)BUFFER_SIZE;

CLA_forceTasks(myCLA0_BASE,CLA_TASKFLAG_1);

WAITSTEP;

y[i] = fResult;

error = fabsf(asin_expected[i]-y[i]);

if(error < 0.1f)

{

pass++;

}

else

{

fail++;

}

}

#if 0

CLA_forceTasks(CLA1_BASE,CLA_TASKFLAG_2);

WAITSTEP;

CLA_forceTasks(CLA1_BASE,CLA_TASKFLAG_3);

WAITSTEP;

CLA_forceTasks(CLA1_BASE,CLA_TASKFLAG_4);

WAITSTEP;

CLA_forceTasks(CLA1_BASE,CLA_TASKFLAG_5);

WAITSTEP;

CLA_forceTasks(CLA1_BASE,CLA_TASKFLAG_6);

WAITSTEP;

CLA_forceTasks(CLA1_BASE,CLA_TASKFLAG_7);

WAITSTEP;

CLA_forceTasks(CLA1_BASE,CLA_TASKFLAG_8);

WAITSTEP;

#endif

}

//

// cla1Isr1 - CLA1 ISR 1

//

__interrupt void cla1Isr1 ()

{

//

// Acknowledge the end-of-task interrupt for task 1

//

Interrupt_clearACKGroup(INTERRUPT_ACK_GROUP11);

//

// Uncomment to halt debugger and stop here

//

// asm(" ESTOP0");

}

//

// cla1Isr2 - CLA1 ISR 2

//

__interrupt void cla1Isr2 ()

{

asm(" ESTOP0");

}

//

// cla1Isr3 - CLA1 ISR 3

//

__interrupt void cla1Isr3 ()

{

asm(" ESTOP0");

}

//

// cla1Isr4 - CLA1 ISR 4

//

__interrupt void cla1Isr4 ()

{

asm(" ESTOP0");

}

//

// cla1Isr5 - CLA1 ISR 5

//

__interrupt void cla1Isr5 ()

{

asm(" ESTOP0");

}

//

// cla1Isr6 - CLA1 ISR 6

//

__interrupt void cla1Isr6 ()

{

asm(" ESTOP0");

}

//

// cla1Isr7 - CLA1 ISR 7

//

__interrupt void cla1Isr7 ()

{

asm(" ESTOP0");

}

//

// cla1Isr8 - CLA1 ISR 8

//

__interrupt void cla1Isr8 ()

{

//

// Acknowledge the end-of-task interrupt for task 8

//

Interrupt_clearACKGroup(INTERRUPT_ACK_GROUP11);

//

// Uncomment to halt debugger and stop here

//

// asm(" ESTOP0");

}

//

// End of File

//

28004x_generic_flash_lnk.cmd代码如下:

MEMORY

{

PAGE 0 :

/* BEGIN is used for the "boot to Flash" bootloader mode */

BEGIN : origin = 0x080000, length = 0x000002

RAMM0 : origin = 0x0000F6, length = 0x00030A

RAMLS0 : origin = 0x008000, length = 0x001000

RAMLS3 : origin = 0x00A000, length = 0x000800

/* RAMLS4 : origin = 0x00A000, length = 0x000800 */

RESET : origin = 0x3FFFC0, length = 0x000002

/* Flash sectors */

/* BANK 0 */

FLASH_BANK0_SEC0 : origin = 0x080002, length = 0x000FFE /* on-chip Flash */

FLASH_BANK0_SEC1 : origin = 0x081000, length = 0x001000 /* on-chip Flash */

FLASH_BANK0_SEC2 : origin = 0x082000, length = 0x001000 /* on-chip Flash */

FLASH_BANK0_SEC3 : origin = 0x083000, length = 0x001000 /* on-chip Flash */

FLASH_BANK0_SEC4 : origin = 0x084000, length = 0x001000 /* on-chip Flash */

FLASH_BANK0_SEC5 : origin = 0x085000, length = 0x001000 /* on-chip Flash */

FLASH_BANK0_SEC6 : origin = 0x086000, length = 0x001000 /* on-chip Flash */

FLASH_BANK0_SEC7 : origin = 0x087000, length = 0x001000 /* on-chip Flash */

// FLASH_BANK0_SEC8 : origin = 0x088000, length = 0x001000 /* on-chip Flash */

FLASH_BANK0_SEC8 : origin = 0x088000, length = 0x000100 /* on-chip Flash */

FLASH_BANK0_SEC81 : origin = 0x088100, length =0x000F00 /* on-chip Flash */ //drc

FLASH_BANK0_SEC9 : origin = 0x089000, length = 0x001000 /* on-chip Flash */

FLASH_BANK0_SEC10 : origin = 0x08A000, length = 0x001000 /* on-chip Flash */

FLASH_BANK0_SEC11 : origin = 0x08B000, length = 0x001000 /* on-chip Flash */

FLASH_BANK0_SEC12 : origin = 0x08C000, length = 0x001000 /* on-chip Flash */

FLASH_BANK0_SEC13 : origin = 0x08D000, length = 0x001000 /* on-chip Flash */

FLASH_BANK0_SEC14 : origin = 0x08E000, length = 0x001000 /* on-chip Flash */

FLASH_BANK0_SEC15 : origin = 0x08F000, length = 0x001000 /* on-chip Flash */

/* BANK 1 */

FLASH_BANK1_SEC0 : origin = 0x090000, length = 0x001000 /* on-chip Flash */

FLASH_BANK1_SEC1 : origin = 0x091000, length = 0x001000 /* on-chip Flash */

FLASH_BANK1_SEC2 : origin = 0x092000, length = 0x001000 /* on-chip Flash */

FLASH_BANK1_SEC3 : origin = 0x093000, length = 0x001000 /* on-chip Flash */

FLASH_BANK1_SEC4 : origin = 0x094000, length = 0x001000 /* on-chip Flash */

FLASH_BANK1_SEC5 : origin = 0x095000, length = 0x001000 /* on-chip Flash */

FLASH_BANK1_SEC6 : origin = 0x096000, length = 0x001000 /* on-chip Flash */

FLASH_BANK1_SEC7 : origin = 0x097000, length = 0x001000 /* on-chip Flash */

FLASH_BANK1_SEC8 : origin = 0x098000, length = 0x001000 /* on-chip Flash */

FLASH_BANK1_SEC9 : origin = 0x099000, length = 0x001000 /* on-chip Flash */

FLASH_BANK1_SEC10 : origin = 0x09A000, length = 0x001000 /* on-chip Flash */

FLASH_BANK1_SEC11 : origin = 0x09B000, length = 0x001000 /* on-chip Flash */

FLASH_BANK1_SEC12 : origin = 0x09C000, length = 0x001000 /* on-chip Flash */

FLASH_BANK1_SEC13 : origin = 0x09D000, length = 0x001000 /* on-chip Flash */

FLASH_BANK1_SEC14 : origin = 0x09E000, length = 0x001000 /* on-chip Flash */

FLASH_BANK1_SEC15 : origin = 0x09F000, length = 0x000FF0 /* on-chip Flash */

// FLASH_BANK1_SEC15_RSVD : origin = 0x09FFF0, length = 0x000010 /* Reserve and do not use for code as per the errata advisory "Memory: Prefetching Beyond Valid Memory" */

PAGE 1 :

BOOT_RSVD : origin = 0x000002, length = 0x0000F1 /* Part of M0, BOOT rom will use this for stack */

RAMM1 : origin = 0x000400, length = 0x0003F8 /* on-chip RAM block M1 */

// RAMM1_RSVD : origin = 0x0007F8, length = 0x000008 /* Reserve and do not use for code as per the errata advisory "Memory: Prefetching Beyond Valid Memory" */

RAMLS1 : origin = 0x009000, length = 0x000800

RAMLS2 : origin = 0x009800, length = 0x000800

RAMLS5 : origin = 0x00A800, length = 0x001800

/* RAMLS5 : origin = 0x00A800, length = 0x002800//shc-yuanlai

RAMLS6 : origin = 0x00B000, length = 0x000800

RAMLS7 : origin = 0x00B800, length = 0x000800 */

RAMGS0 : origin = 0x00C000, length = 0x002000

RAMGS1 : origin = 0x00E000, length = 0x002000

RAMGS2 : origin = 0x010000, length = 0x002000

RAMGS3 : origin = 0x012000, length = 0x001FF8

// RAMGS3_RSVD : origin = 0x013FF8, length = 0x000008 /* Reserve and do not use for code as per the errata advisory "Memory: Prefetching Beyond Valid Memory" */

CLA1_MSGRAMLOW : origin = 0x001480, length = 0x000080

CLA1_MSGRAMHIGH : origin = 0x001500, length = 0x000080

}

SECTIONS

{

codestart : > FLASH_BANK0_SEC8, PAGE = 0, ALIGN(4) /*BEGIN*/

.mcuver1 : > FLASH_BANK0_SEC81, PAGE = 0, ALIGN(4)

.text : >> FLASH_BANK0_SEC10 | FLASH_BANK0_SEC11 | FLASH_BANK0_SEC12 | FLASH_BANK0_SEC13 | FLASH_BANK0_SEC14 | FLASH_BANK0_SEC15 | FLASH_BANK1_SEC0 | FLASH_BANK1_SEC1 , PAGE = 0, ALIGN(4) /*| FLASH_BANK0_SEC8*/

.cinit : > FLASH_BANK0_SEC9, PAGE = 0, ALIGN(4)

.switch : > FLASH_BANK0_SEC9, PAGE = 0, ALIGN(4)

.reset : > RESET, PAGE = 0, TYPE = DSECT /* not used, */

.stack : > RAMM1, PAGE = 1

#if defined(__TI_EABI__)

.init_array : > FLASH_BANK0_SEC9, PAGE = 0, ALIGN(4)

.bss : > RAMLS5, PAGE = 1

.bss:output : > RAMLS3, PAGE = 0

.bss:cio : > RAMLS0, PAGE = 0

.data : > RAMLS5, PAGE = 1

.sysmem : > RAMLS5, PAGE = 1

/* Initalized sections go in Flash */

.const : > FLASH_BANK0_SEC12, PAGE = 0, ALIGN(4)

#else

.pinit : > FLASH_BANK0_SEC9, PAGE = 0, ALIGN(4)

.ebss : > RAMLS5, PAGE = 1

.esysmem : > RAMLS5, PAGE = 1

.cio : > RAMLS0, PAGE = 0

.econst : > FLASH_BANK0_SEC12, PAGE = 0, ALIGN(4)

#endif

ramgs0 : > RAMGS0, PAGE = 1

ramgs1 : > RAMGS1, PAGE = 1

ramgs2 : > RAMGS2, PAGE = 1

ramgs3 : > RAMGS3, PAGE = 1

#if defined(__TI_EABI__)

/* CLA specific sections */

Cla1Prog : LOAD = FLASH_BANK0_SEC11,

RUN = RAMLS0,

LOAD_START(Cla1ProgLoadStart),

RUN_START(Cla1ProgRunStart),

LOAD_SIZE(Cla1ProgLoadSize),

PAGE = 0, ALIGN(4)

#else

/* CLA specific sections */

Cla1Prog : LOAD = FLASH_BANK0_SEC11,

RUN = RAMLS0,

LOAD_START(_Cla1ProgLoadStart),

RUN_START(_Cla1ProgRunStart),

LOAD_SIZE(_Cla1ProgLoadSize),

PAGE = 0, ALIGN(4)

#endif

Cla1ToCpuMsgRAM : > CLA1_MSGRAMLOW, PAGE = 1

CpuToCla1MsgRAM : > CLA1_MSGRAMHIGH, PAGE = 1

#if defined(__TI_EABI__)

.TI.ramfunc : LOAD = FLASH_BANK0_SEC9,

RUN = RAMLS0,

LOAD_START(RamfuncsLoadStart),

LOAD_SIZE(RamfuncsLoadSize),

LOAD_END(RamfuncsLoadEnd),

RUN_START(RamfuncsRunStart),

RUN_SIZE(RamfuncsRunSize),

RUN_END(RamfuncsRunEnd),

PAGE = 0, ALIGN(4)

#else

.TI.ramfunc : LOAD = FLASH_BANK0_SEC9,

RUN = RAMLS0,

LOAD_START(_RamfuncsLoadStart),

LOAD_SIZE(_RamfuncsLoadSize),

LOAD_END(_RamfuncsLoadEnd),

RUN_START(_RamfuncsRunStart),

RUN_SIZE(_RamfuncsRunSize),

RUN_END(_RamfuncsRunEnd),

PAGE = 0, ALIGN(4)

#endif

.scratchpad : > RAMLS1, PAGE = 1

.bss_cla : > RAMLS1, PAGE = 1

Cla1DataRam : > RAMLS2, PAGE = 1

cla_shared : > RAMLS1, PAGE = 1

CLADataLS1 : > RAMLS1, PAGE = 1

#if defined(__TI_EABI__)

.const_cla : LOAD = FLASH_BANK0_SEC10,

RUN = RAMLS3,

RUN_START(Cla1ConstRunStart),

LOAD_START(Cla1ConstLoadStart),

LOAD_SIZE(Cla1ConstLoadSize),

PAGE = 0, ALIGN(4)

#else

.const_cla : LOAD = FLASH_BANK0_SEC10,

RUN = RAMLS3,

RUN_START(_Cla1ConstRunStart),

LOAD_START(_Cla1ConstLoadStart),

LOAD_SIZE(_Cla1ConstLoadSize),

PAGE = 0, ALIGN(4)

#endif

}

/*

//===========================================================================

// End of file.

//===========================================================================

*/