Part Number: TMS320F280021-Q1

Other Parts Discussed in Thread: TMS320F280021

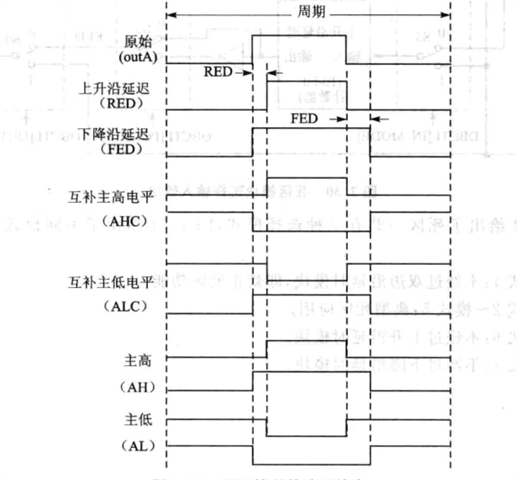

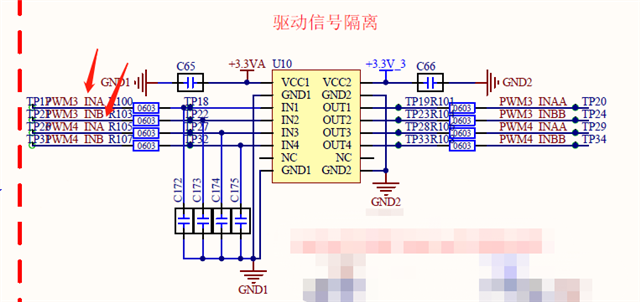

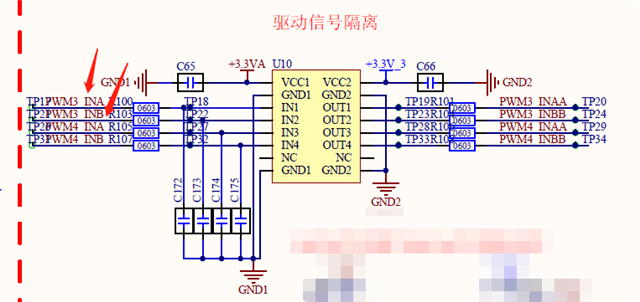

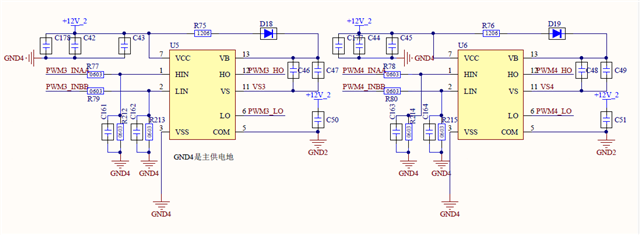

问题:用TMS320F280021做LLC充电过程,ePWM3和ePwm4为驱动H桥LLC,PWM工作频率为80K~150K,为软件设置的上下限值,谐振工作频率为90KHZ。当LLC工作过程进行调节频率从85K往下调节,接近80K时,偶尔有几率有发生半桥上下MOS管驱动同高现象,非百分百,MOS管直通短路,管子烧坏。请问各位大神帮忙审核下配置是否有问题?感谢!

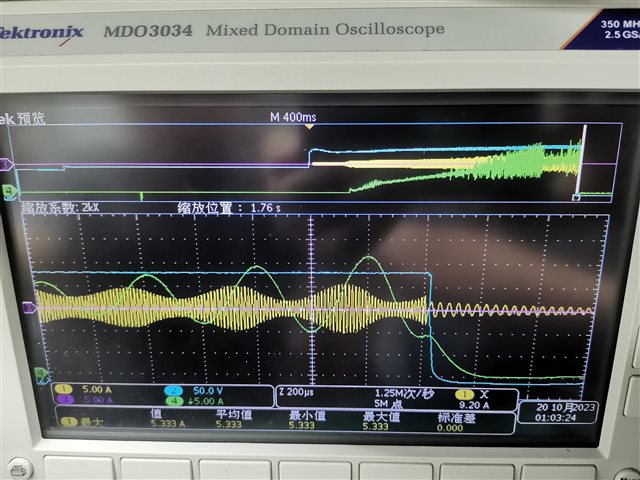

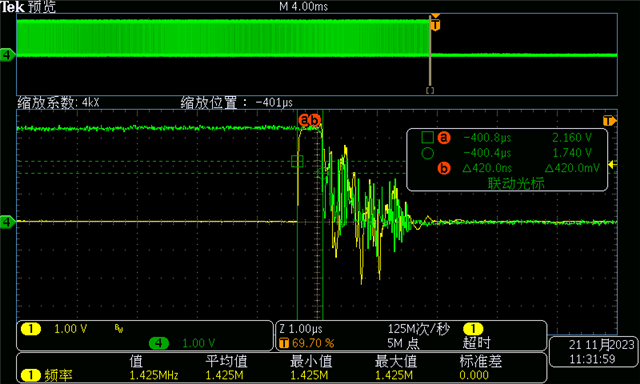

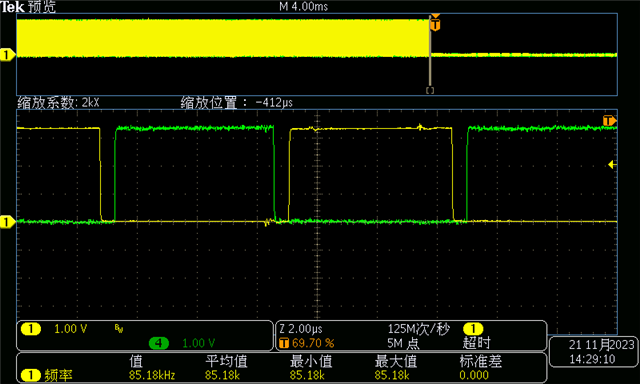

波形如下:

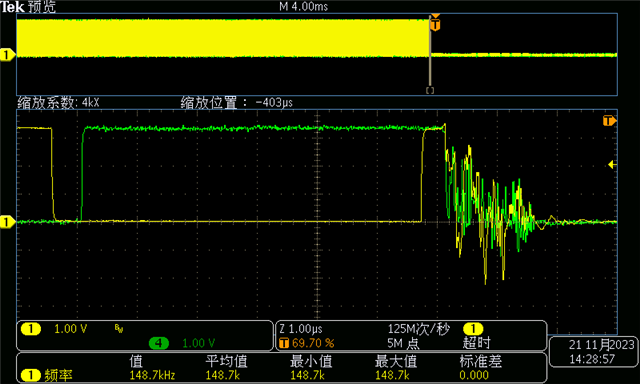

短路前一时刻的驱动波形和频率:

以下为PWM配置代码:

void UserSetEPWM()

{

EALLOW;

CpuSysRegs.PCLKCR0.bit.TBCLKSYNC = 0;

EDIS;

EALLOW;

GpioCtrlRegs.GPHAMSEL.bit.GPIO242 = 0;

GpioCtrlRegs.GPHQSEL2.bit.GPIO242 = 3;

InputXbarRegs.INPUT1SELECT = 242;

GpioCtrlRegs.GPHLOCK.bit.GPIO242 = 1;

GpioCtrlRegs.GPHCR.bit.GPIO242 = 1;

InputXbarRegs.INPUTSELECTLOCK.bit.INPUT1SELECT = 1;

EPwm1Regs.TZSEL.bit.OSHT1 = TZ_ENABLE;

EPwm2Regs.TZSEL.bit.OSHT1 = TZ_ENABLE;

EPwm3Regs.TZSEL.bit.OSHT1 = TZ_ENABLE;

EPwm4Regs.TZSEL.bit.OSHT1 = TZ_ENABLE;

EPwm1Regs.TZSEL.bit.OSHT5 = TZ_ENABLE;

EPwm2Regs.TZSEL.bit.OSHT5 = TZ_ENABLE;

EPwm3Regs.TZSEL.bit.OSHT5 = TZ_ENABLE;

EPwm4Regs.TZSEL.bit.OSHT5 = TZ_ENABLE;

EPwm1Regs.TZSEL.bit.OSHT6 = TZ_ENABLE;

EPwm2Regs.TZSEL.bit.OSHT6 = TZ_ENABLE;

EPwm3Regs.TZSEL.bit.OSHT6 = TZ_ENABLE;

EPwm4Regs.TZSEL.bit.OSHT6 = TZ_ENABLE;

EPwm1Regs.TZCTL.bit.TZA = TZ_FORCE_LO;

EPwm1Regs.TZCTL.bit.TZB = TZ_FORCE_LO;

EPwm2Regs.TZCTL.bit.TZA = TZ_FORCE_LO;

EPwm2Regs.TZCTL.bit.TZB = TZ_FORCE_LO;

EPwm3Regs.TZCTL.bit.TZA = TZ_FORCE_LO;

EPwm3Regs.TZCTL.bit.TZB = TZ_FORCE_LO;

EPwm4Regs.TZCTL.bit.TZA = TZ_FORCE_LO;

EPwm4Regs.TZCTL.bit.TZB = TZ_FORCE_LO;

EPwm1Regs.TZFRC.bit.OST = 1;

EPwm2Regs.TZFRC.bit.OST = 1;

EPwm3Regs.TZFRC.bit.OST = 1;

EPwm4Regs.TZFRC.bit.OST = 1;

EPwm1Regs.GLDCFG.all = 0x07FF;

EPwm1Regs.GLDCTL.bit.GLDMODE = 6;

EPwm1Regs.GLDCTL.bit.OSHTMODE = 1;

EPwm1Regs.GLDCTL.bit.GLD = 1;

EPwm1Regs.EPWMXLINK.bit.GLDCTL2LINK = 0;

EPwm2Regs.GLDCFG.all = 0x07FF;

EPwm2Regs.GLDCTL.bit.GLDMODE = 6;

EPwm2Regs.GLDCTL.bit.OSHTMODE = 1;

EPwm2Regs.GLDCTL.bit.GLD = 1;

EPwm2Regs.EPWMXLINK.bit.GLDCTL2LINK = 0;

EPwm3Regs.GLDCFG.all = 0x07FF;

EPwm3Regs.GLDCTL.bit.GLDMODE = 6;

EPwm3Regs.GLDCTL.bit.OSHTMODE = 1;

EPwm3Regs.GLDCTL.bit.GLD = 1;

EPwm3Regs.EPWMXLINK.bit.GLDCTL2LINK = 0;

EPwm4Regs.GLDCFG.all = 0x07FF;

EPwm4Regs.GLDCTL.bit.GLDMODE = 6;

EPwm4Regs.GLDCTL.bit.OSHTMODE = 1;

EPwm4Regs.GLDCTL.bit.GLD = 1;

EPwm4Regs.EPWMXLINK.bit.GLDCTL2LINK = 0;

EDIS;

EPwm1Regs.TBPRD = EPWMPeriod;

EPwm1Regs.TBCTL.bit.CLKDIV = TB_DIV1; // TBCLK = SYSCLKOUT /(HSPCLKDIV ×CLKDIV)

EPwm1Regs.TBCTL.bit.HSPCLKDIV = TB_DIV1;

EPwm1Regs.TBCTL.bit.PHSDIR = TB_UP;

EPwm1Regs.TBCTL.bit.PRDLD = TB_SHADOW;

EPwm1Regs.TBCTL.bit.PHSEN = TB_ENABLE; //使能同步

EPwm1Regs.TBPHS.bit.TBPHS = 0;

EPwm1Regs.TBCTL.bit.CTRMODE = TB_COUNT_UPDOWN; // Count updown

EPwm1Regs.EPWMSYNCINSEL.bit.SEL = SYNC_IN_SRC_DISABLE_ALL;

EPwm1Regs.EPWMSYNCOUTEN.bit.ZEROEN = SYNC_OUT_SRC_ENABLE;

EPwm2Regs.TBPRD = EPWMPeriod;

EPwm2Regs.TBCTL.bit.CLKDIV = TB_DIV1; // TBCLK = SYSCLKOUT /(HSPCLKDIV ×CLKDIV)

EPwm2Regs.TBCTL.bit.HSPCLKDIV = TB_DIV1;

EPwm2Regs.TBCTL.bit.PHSDIR = TB_UP;

EPwm2Regs.TBCTL.bit.PRDLD = TB_SHADOW;

EPwm2Regs.TBCTL.bit.PHSEN = TB_ENABLE;

EPwm2Regs.TBPHS.bit.TBPHS = 2;

EPwm2Regs.TBCTL.bit.CTRMODE = TB_COUNT_UPDOWN; // Count updown

EPwm2Regs.EPWMSYNCINSEL.bit.SEL = SYNC_IN_SRC_SYNCOUT_EPWM1;

EPwm3Regs.TBPRD = EPWMPeriod;

EPwm3Regs.TBCTL.bit.CLKDIV = TB_DIV1; // TBCLK = SYSCLKOUT /(HSPCLKDIV ×CLKDIV)

EPwm3Regs.TBCTL.bit.HSPCLKDIV = TB_DIV1;

EPwm3Regs.TBCTL.bit.PHSDIR = TB_UP;

EPwm3Regs.TBCTL.bit.PRDLD = TB_SHADOW;

EPwm3Regs.TBCTL.bit.PHSEN = TB_ENABLE;

EPwm3Regs.TBPHS.bit.TBPHS = 3; //补偿10ns数字隔离器延迟

EPwm3Regs.TBCTL.bit.CTRMODE = TB_COUNT_UPDOWN; // Count updown

EPwm3Regs.EPWMSYNCINSEL.bit.SEL = SYNC_IN_SRC_SYNCOUT_EPWM1;

EPwm4Regs.TBPRD = EPWMPeriod;

EPwm4Regs.TBCTL.bit.CLKDIV = TB_DIV1; // TBCLK = SYSCLKOUT /(HSPCLKDIV ×CLKDIV)

EPwm4Regs.TBCTL.bit.HSPCLKDIV = TB_DIV1;

EPwm4Regs.TBCTL.bit.PHSDIR = TB_UP;

EPwm4Regs.TBCTL.bit.PRDLD = TB_SHADOW;

EPwm4Regs.TBCTL.bit.PHSEN = TB_ENABLE;

EPwm4Regs.TBPHS.bit.TBPHS = 3; //补偿10ns数字隔离器延迟

EPwm4Regs.TBCTL.bit.CTRMODE = TB_COUNT_UPDOWN; // Count updown

EPwm4Regs.EPWMSYNCINSEL.bit.SEL = SYNC_IN_SRC_SYNCOUT_EPWM1;

EPwm5Regs.TBPRD = 1000;

EPwm5Regs.TBCTL.bit.CLKDIV = TB_DIV1; // TBCLK = SYSCLKOUT /(HSPCLKDIV ×CLKDIV)

EPwm5Regs.TBCTL.bit.HSPCLKDIV = TB_DIV1;

EPwm5Regs.TBCTL.bit.PHSDIR = TB_UP;

EPwm5Regs.TBCTL.bit.PRDLD = TB_SHADOW;

EPwm5Regs.TBCTL.bit.PHSEN = TB_DISABLE;

// EPwm5Regs.TBPHS.bit.TBPHS = 2; //补偿10ns数字隔离器延迟

EPwm5Regs.TBCTL.bit.CTRMODE = TB_COUNT_UPDOWN; // Count updown

EPwm5Regs.EPWMSYNCINSEL.bit.SEL = SYNC_IN_SRC_DISABLE_ALL;

//计数比较模块设定

EPwm1Regs.TBCTR = 0; //计数初值为0

EPwm1Regs.CMPA.bit.CMPA = EPWMPeriod_DIV2 - LeastTime_LLC;

EPwm1Regs.CMPB.bit.CMPB = EPWMPeriod_DIV2 + LeastTime_LLC;

EPwm1Regs.CMPCTL.bit.LOADAMODE = CC_CTR_ZERO;

EPwm1Regs.CMPCTL.bit.LOADBMODE = CC_CTR_ZERO;

EPwm1Regs.CMPCTL.bit.SHDWAMODE = CC_SHADOW;

EPwm1Regs.CMPCTL.bit.SHDWBMODE = CC_SHADOW;

EPwm2Regs.TBCTR = 0; //计数初值为0

EPwm2Regs.CMPA.bit.CMPA = EPWMPeriod_DIV2 - LeastTime_LLC;

EPwm2Regs.CMPB.bit.CMPB = EPWMPeriod_DIV2 + LeastTime_LLC;

EPwm2Regs.CMPCTL.bit.LOADAMODE = CC_CTR_ZERO;

EPwm2Regs.CMPCTL.bit.LOADBMODE = CC_CTR_ZERO;

EPwm2Regs.CMPCTL.bit.SHDWAMODE = CC_SHADOW;

EPwm2Regs.CMPCTL.bit.SHDWBMODE = CC_SHADOW;

EPwm3Regs.TBCTR = 0; //计数初值为0

EPwm3Regs.CMPA.bit.CMPA = EPWMPeriod_DIV2 - LeastTime_LLC;

EPwm3Regs.CMPB.bit.CMPB = EPWMPeriod_DIV2 + LeastTime_LLC;

EPwm3Regs.CMPCTL.bit.LOADAMODE = CC_CTR_ZERO;

EPwm3Regs.CMPCTL.bit.LOADBMODE = CC_CTR_ZERO;

EPwm3Regs.CMPCTL.bit.SHDWAMODE = CC_SHADOW;

EPwm3Regs.CMPCTL.bit.SHDWBMODE = CC_SHADOW;

EPwm4Regs.TBCTR = 0; //计数初值为0

EPwm4Regs.CMPA.bit.CMPA = EPWMPeriod_DIV2 - LeastTime_LLC;

EPwm4Regs.CMPB.bit.CMPB = EPWMPeriod_DIV2 + LeastTime_LLC;

EPwm4Regs.CMPCTL.bit.LOADAMODE = CC_CTR_ZERO;

EPwm4Regs.CMPCTL.bit.LOADBMODE = CC_CTR_ZERO;

EPwm4Regs.CMPCTL.bit.SHDWAMODE = CC_SHADOW;

EPwm4Regs.CMPCTL.bit.SHDWBMODE = CC_SHADOW;

EPwm5Regs.TBCTR = 0; //计数初值为0

// EPwm5Regs.CMPA.bit.CMPA = 0;

// EPwm5Regs.CMPCTL.bit.LOADAMODE = CC_CTR_ZERO;

// EPwm5Regs.CMPCTL.bit.SHDWAMODE = CC_SHADOW;

// AQ模块设定

EPwm1Regs.AQCTLA.bit.CAU = AQ_SET;

EPwm1Regs.AQCTLA.bit.CBU = AQ_CLEAR;

EPwm1Regs.AQCTLB.bit.CBD = AQ_SET;

EPwm1Regs.AQCTLB.bit.CAD = AQ_CLEAR;

EPwm1Regs.AQCTLA.bit.ZRO = AQ_CLEAR;

EPwm1Regs.AQCTLB.bit.ZRO = AQ_CLEAR;

EPwm2Regs.AQCTLB.bit.CAU = AQ_SET;

EPwm2Regs.AQCTLB.bit.CBU = AQ_CLEAR;

EPwm2Regs.AQCTLA.bit.CBD = AQ_SET;

EPwm2Regs.AQCTLA.bit.CAD = AQ_CLEAR;

EPwm2Regs.AQCTLA.bit.ZRO = AQ_CLEAR;

EPwm2Regs.AQCTLB.bit.ZRO = AQ_CLEAR;

EPwm3Regs.AQCTLA.bit.CAU = AQ_SET;

EPwm3Regs.AQCTLA.bit.CBU = AQ_CLEAR;

EPwm3Regs.AQCTLB.bit.CBD = AQ_SET;

EPwm3Regs.AQCTLB.bit.CAD = AQ_CLEAR;

EPwm3Regs.AQCTLA.bit.ZRO = AQ_CLEAR;

EPwm3Regs.AQCTLB.bit.ZRO = AQ_CLEAR;

EPwm4Regs.AQCTLB.bit.CAU = AQ_SET;

EPwm4Regs.AQCTLB.bit.CBU = AQ_CLEAR;

EPwm4Regs.AQCTLA.bit.CBD = AQ_SET;

EPwm4Regs.AQCTLA.bit.CAD = AQ_CLEAR;

EPwm4Regs.AQCTLA.bit.ZRO = AQ_CLEAR;

EPwm4Regs.AQCTLB.bit.ZRO = AQ_CLEAR;

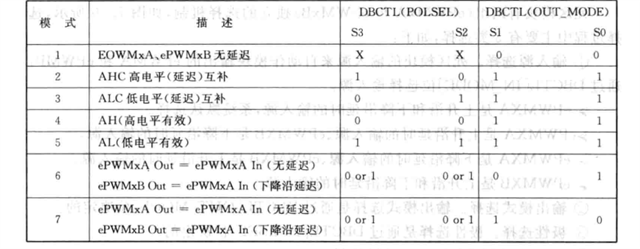

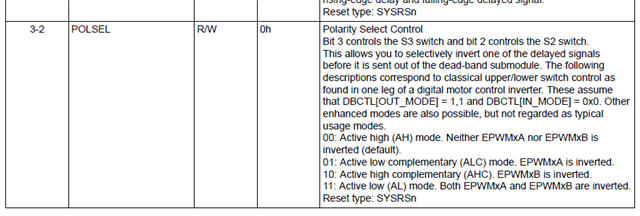

//DB死区模块设定

EPwm1Regs.DBCTL.bit.OUT_MODE = DB_DISABLE;

EPwm2Regs.DBCTL.bit.OUT_MODE = DB_DISABLE;

EPwm3Regs.DBCTL.bit.OUT_MODE = DB_DISABLE;

EPwm4Regs.DBCTL.bit.OUT_MODE = DB_DISABLE;

EPwm1Regs.GLDCTL2.bit.GFRCLD = 1;

EPwm5Regs.ETSEL.bit.SOCAEN = 1; // 1 Enable the ADC Start of Conversion B (EPWMxSOCB) Pulse, Enable EPWMxSOCB pulse.

EPwm5Regs.ETSEL.bit.SOCASEL = ET_CTR_ZERO; //PRD 触发ADC_B

EPwm5Regs.ETPS.bit.SOCAPRD = ET_1ST;

// EPwm1Regs.ETSEL.bit.INTEN = 1; // 1 Enable the ADC Start of Conversion B (EPWMxSOCB) Pulse, Enable EPWMxSOCB pulse.

// EPwm1Regs.ETSEL.bit.INTSEL = ET_CTR_ZERO; //PRD 触发ADC_B

// EPwm1Regs.ETPS.bit.INTPRD = ET_1ST;

EALLOW;

CpuSysRegs.PCLKCR0.bit.TBCLKSYNC = 1;

EDIS;

}

以下为PWM转载代码:

void loadpwm()

{

F_SW = CC_PID.PIDU; //PI计算值

F_SW = __fmin(150,F_SW);

F_SW = __fmax(80,F_SW);

EPWMPeriod = 50000 / F_SW;

EPWMPeriod_DIV2 = EPWMPeriod / 2;

LLC_Hduty_EPWM = LLC_duty * EPWMPeriod_DIV2;

if( LLC_Hduty_EPWM > EPWMPeriod_DIV2 - 25 )

{

LLC_Hduty_EPWM = EPWMPeriod_DIV2 - 25;

}

EPWMPeriod = EPWM_Cal_SW / F_SW;

EPWMPeriod_DIV2 = EPWMPeriod / 2;

EPWMPeriod = EPWMPeriod_DIV2 * 2;

F_Int = 50;

T_Ctrl = 0.001f/F_Int;

EPwm3Regs.TBPRD = EPWMPeriod; //Period of TB = 10kHz

EPwm4Regs.TBPRD = EPWMPeriod; //Period of TB = 10kHz

EPwm3Regs.CMPA.bit.CMPA = EPWMPeriod_DIV2 - LLC_Hduty_EPWM;

EPwm3Regs.CMPB.bit.CMPB = EPWMPeriod_DIV2 + LLC_Hduty_EPWM;

EPwm4Regs.CMPA.bit.CMPA = EPWMPeriod_DIV2 - LLC_Hduty_EPWM;

EPwm4Regs.CMPB.bit.CMPB = EPWMPeriod_DIV2 + LLC_Hduty_EPWM;

EPwm1Regs.GLDCTL2.bit.OSHTLD = 1;

}