Part Number: TMS320F280049C

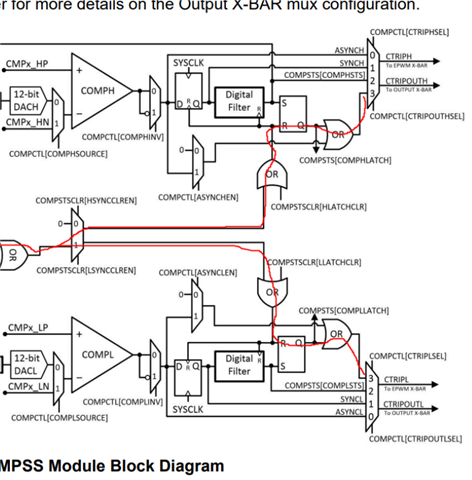

前几天提过一个问题,cmpss口无输出,那个问题最后定位到是配置问题。

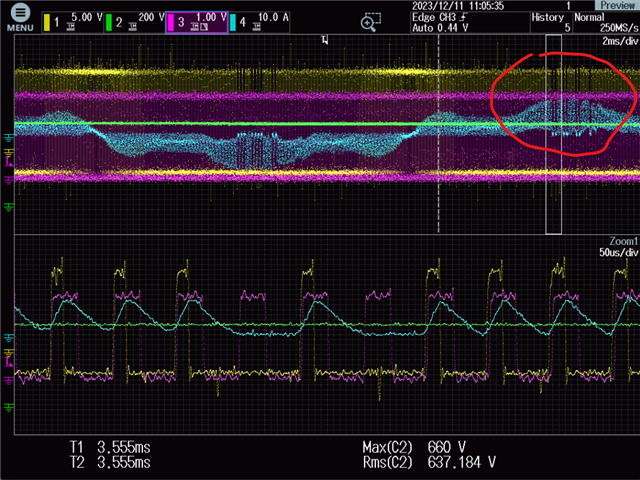

现在已经出来CBC的波形,但是和理论分析不完全一致。

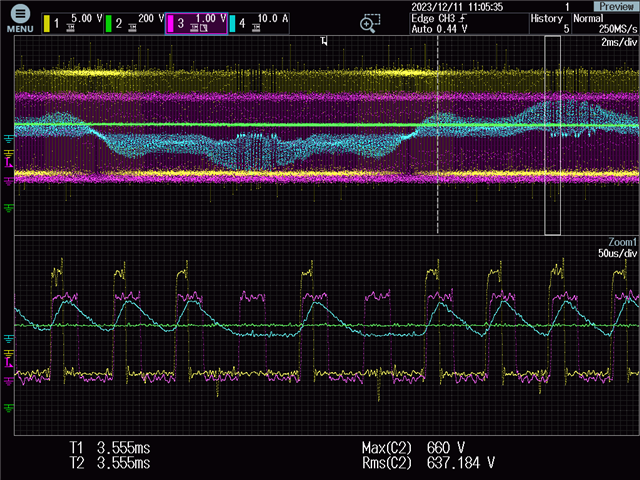

波形1:1通道为PFC驱动,3通道为进中断(高电平)和出中断(低电平),4通道为电感电流波形。

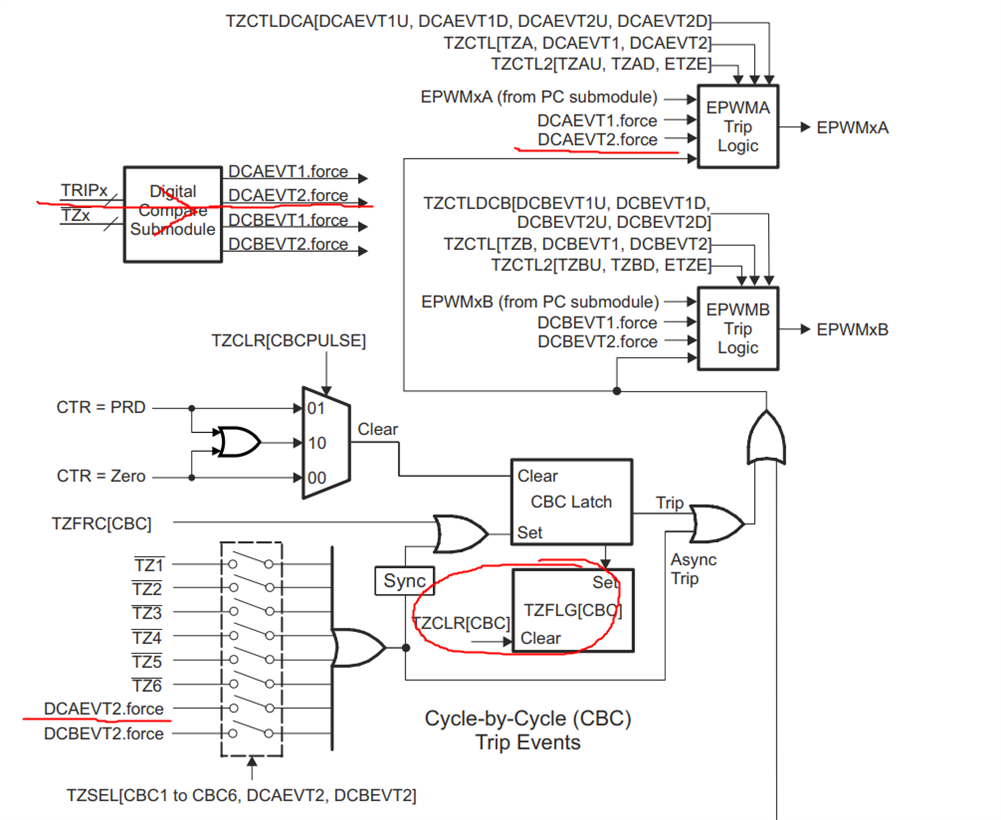

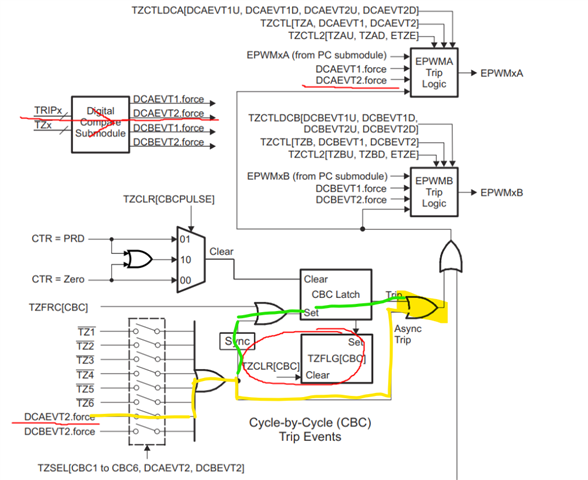

我用的是TRIP5触发DCAEVT2做CBC。

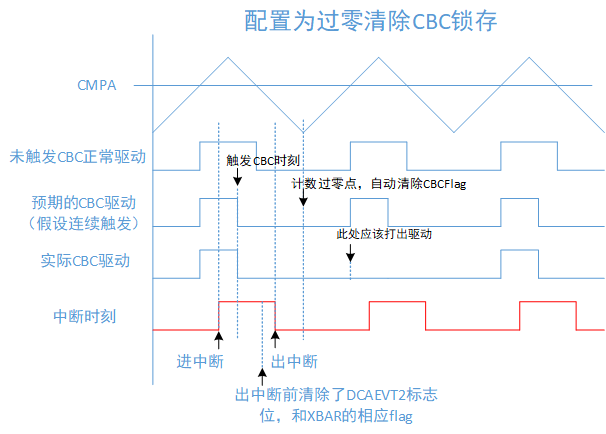

不一致的地方在于,我配置的是在计数过零的时候清除CBC锁存,理论上下一周期应该直接打出驱动,而实际测试多封了一个中断的驱动。

理论分析逻辑:

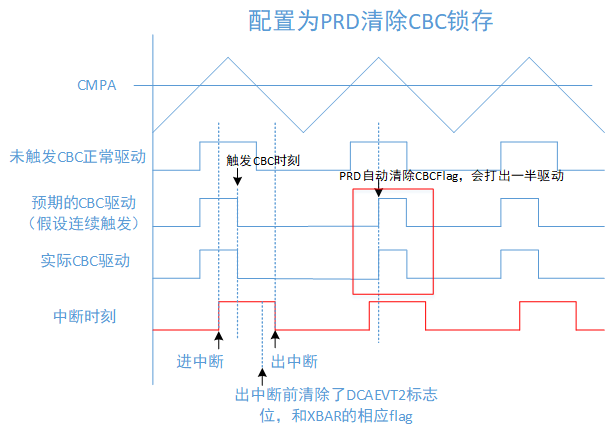

然后我做了对比试验,把 过零清除CBC锁存 改为 PRD清除CBC锁存,实际测试的波形却又是符合分析的

实际测试波形(由于重新打驱动后电感电流未触发到CBC,所以不是连续封波:

理论分析:

从示波器图片里可以看出重新打驱动时确实是只打了一半驱动。

想请教一下TI的工程师,出现这种情况的原因是为什么?和什么寄存器配置相关?

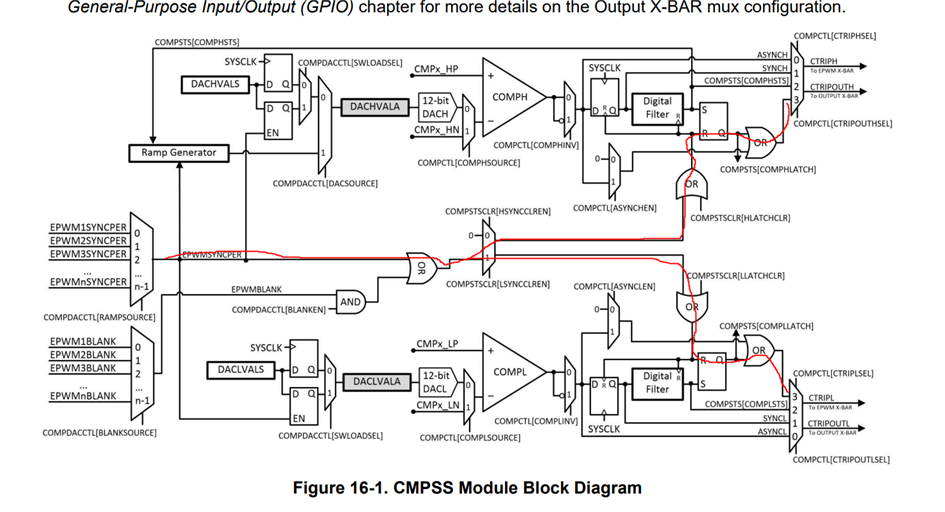

还有想问一下,datasheet中的这张图,左边的Trip事件触发后产生DCAEVT2.force,然后CBC latch模块会产生锁存标志位。由于此时封了驱动,电感电流直接下降,那么CMPSS模块的输出CTRIPH/L 会改变(这个自动清除也有相应函数配置),随之TRIP事件消除,DCAEVT2.force也消除,直到TZCLR(CBCPULSE)配置的ZERO或PRD起作用,自动清除CBC锁存恢复驱动。

那么是不是有可能CMPSS的CTRIPH/L的自动清除会影响到最后的驱动打出。

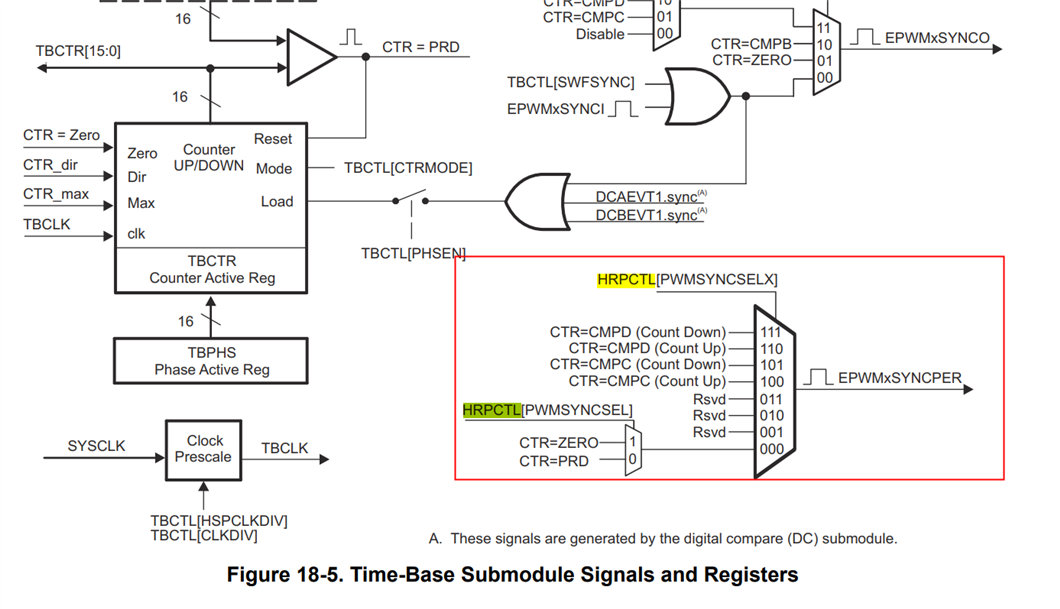

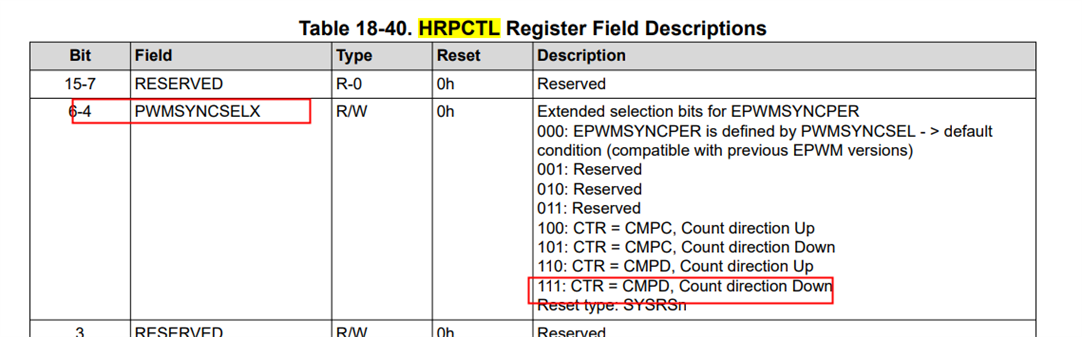

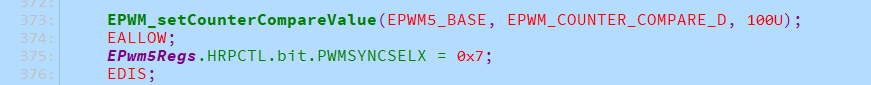

程序里使能了CMPSS的自动清除,CMPSS_enableLatchResetOnPWMSYNCLow(base);

base用的是EPWM5,那也就是说是EPWM5的同步脉冲到来才会去清,而EPWM5的同步脉冲又恰好是过零点,有没有可能是这个原因呢?