Part Number: TMS320F280025

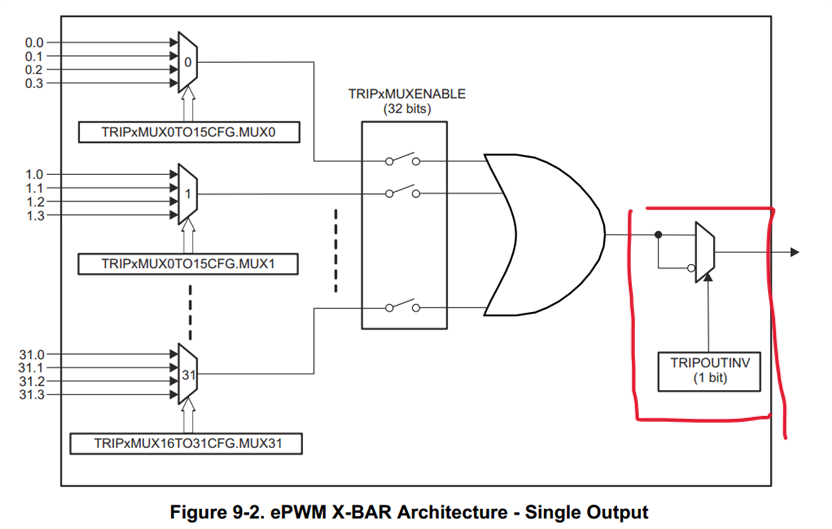

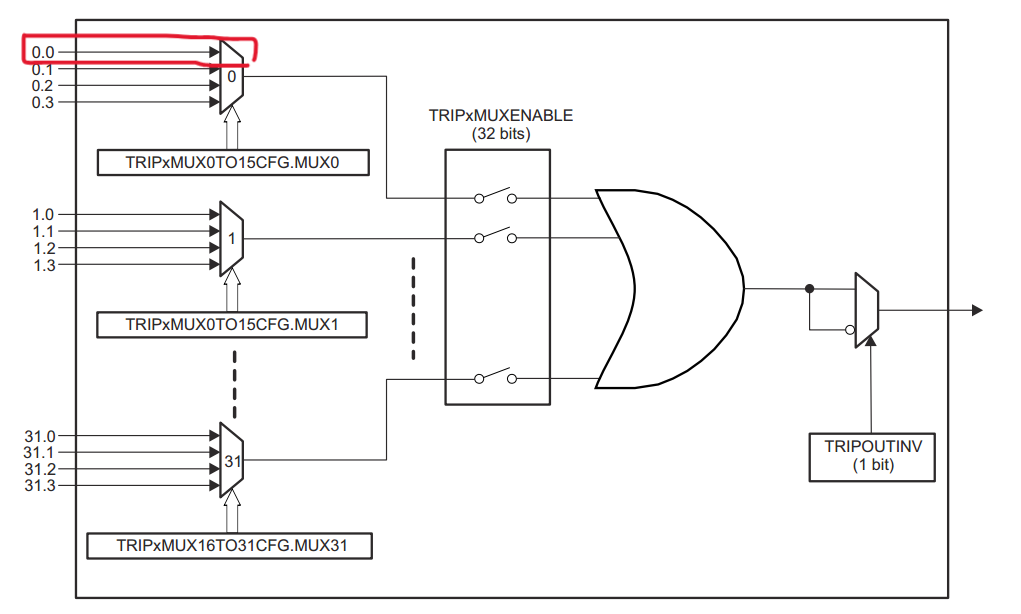

应届生这段时间在配置从CMPSS3->EPWMXBAR->DC(DCAEVT1)->TZ(EPWMA封波)的硬件过流保护,但是一直没有得到想要的封波效果。所以逐一排查问题,我在EPwmXbarRegs.TRIPOUTINV.bit.TRIP4处强制寄予一个高电平

在最终的OST与DCAEVT1处能够实现跳闸事件触发,OST.FLAG和DCAEVT1.FLAG都会置1,这说明DC模块和TZ模块的配置都是正确的,但是如果取消这个强制高电平通过CMPSS的CTRIPH去进行跳闸验证时,OST与DCAEVT1的跳闸事件无法被触发。

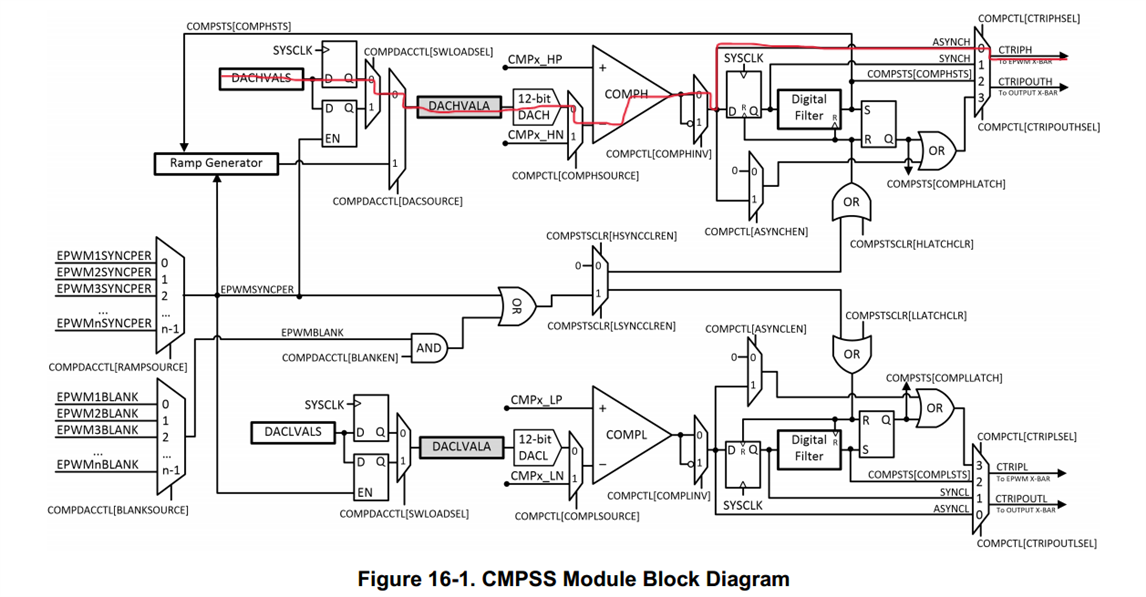

那是不是可以证明从CMPSS3->EPWMXBAR这一部分的某个配置存在问题?红色线是我配置的路线

我的问题有如下几个:

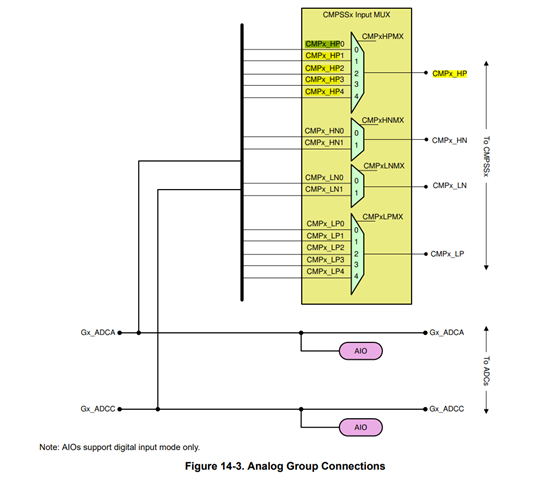

① CMPSS3的比较器正向输入端CMP3HP是不是只需配置AnalogSubsysRegs.CMPHPMXSEL.bit.CMP3HPMXSEL = 1;(此处选择输入为C2)即可?还有没有别的相关配置?如果没有的话是不是直接在C2引脚处外接电源提供电压即可?

②CMPSS3的输出CTRIPH是不是直接接入红色线标注部分?如果不是的话中间还需要配置什么呢?此处我的配置为

EPwmXbarRegs.TRIP4MUX0TO15CFG.bit.MUX4 = 0; // MUX4=0 CMPSS3.CTRIPH

EPwmXbarRegs.TRIP4MUXENABLE.bit.MUX4 = 1; //复用开关使能

③ 烦请各位大神前辈能否帮助审视一下我的CMPSS部分和EPWMXBAR部分是否还有哪里配置不正确或者疏漏 十分感谢!!!

EALLOW;

Cmpss3Regs.COMPDACCTL.bit.DACSOURCE = 0; //DAC更新数据来自于其影子寄存器

Cmpss3Regs.COMPDACCTL.bit.SELREF = 0; //VDDA作为DAC的参考电压

Cmpss3Regs.COMPDACCTL.bit.SWLOADSEL = 0; //使用系统时钟同步DAC

Cmpss3Regs.COMPCTL.bit.COMPDACE = 1; //比较器DAC使能

Cmpss3Regs.COMPCTL.bit.COMPHSOURCE = 0; //高侧比较器方向输入端为DAC

Cmpss3Regs.COMPCTL.bit.COMPHINV = 0; //比较器输出不反相

Cmpss3Regs.COMPCTL.bit.ASYNCHEN = 0; // 异步比较器输出不馈入OR门与锁存数字滤波器输出

Cmpss3Regs.DACHVALS.bit.DACVAL = 434; //配置DAC的影子寄存器值

//输出端

Cmpss3Regs.COMPCTL.bit.CTRIPOUTHSEL = 0;

Cmpss3Regs.COMPCTL.bit.CTRIPHSEL = 0; //比较器输出非同步非滤波信号

Cmpss3Regs.COMPHYSCTL.bit.COMPHYS = 4; //设置典型的滞环宽度

EPwmXbarRegs.TRIP4MUX0TO15CFG.bit.MUX4 = 1; // MUX4=0 CMPSS3.CTRIPH

EPwmXbarRegs.TRIP4MUXENABLE.bit.MUX4 = 1; //复用开关使能

//CMP3HP输入信号

AnalogSubsysRegs.CMPHPMXSEL.bit.CMP3HPMXSEL = 1; //选择C2引脚作为高侧比较器3的同向输入端

EDIS;