Part Number: TMS320F280049C

Other Parts Discussed in Thread: TIDA-010231

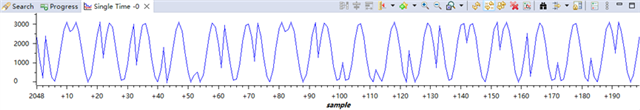

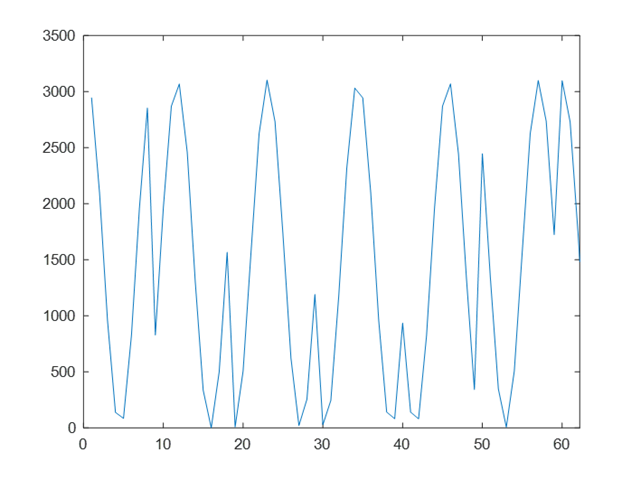

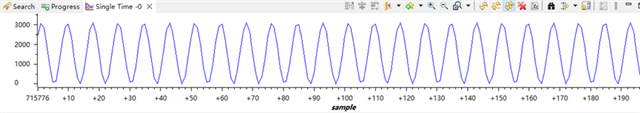

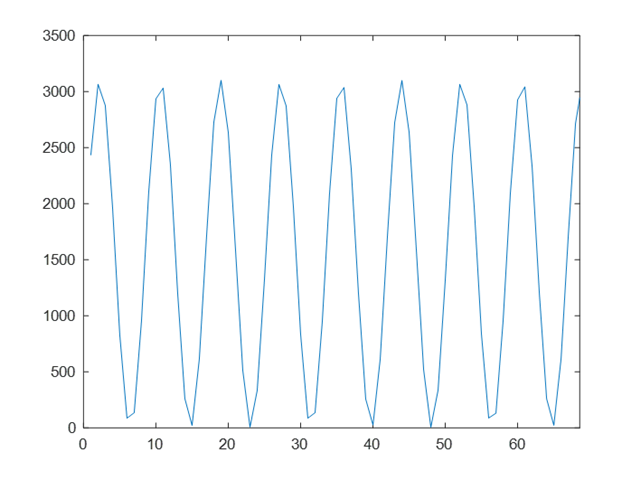

程序中使用了DMA通道进行数据搬运,但是我的问题是程序中有没有数据锁存,如果没有,程序是如何确保fft分析的数据是实时数据而不是上一个窗口的数据。

void ad_acquire_data(int16_t* pAdcDataArr)

{

uint16_t idx;

for (idx = 0; idx < ADSAMPLE_SIZE; idx++)

{

test_input[2 * idx] = (int32_t) pAdcDataArr[idx];

test_input[2 * idx + 1] = 0;

}

}

这个函数是如何读取dma搬运数据结果的,搬运的结果是否为adc实时采样结果,并且这组数据到fft输入口时,数据是否还在发生改变?