Part Number: TMS320F280039C

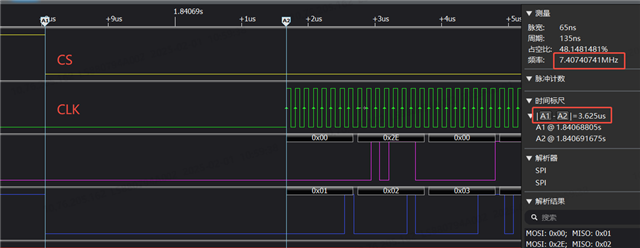

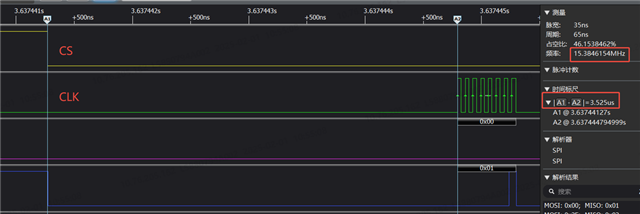

现在使用硬件spi时发现修改时钟频率能上去,但是CS脚拉低之后等待较长时间后CLK才开始改变,导致时钟频率改变后总体的SPI通信时间并没有改变,不知道有没有方法可以设置一下,参考以下图片。

可以看到时钟改变后并没有影响整体通信时间

使用的函数为extern void

SPI_pollingFIFOTransaction(uint32_t base, uint16_t charLength,

uint16_t *pTxBuffer, uint16_t *pRxBuffer,

uint16_t numOfWords, uint16_t txDelay);