Part Number: MSP430F5438A

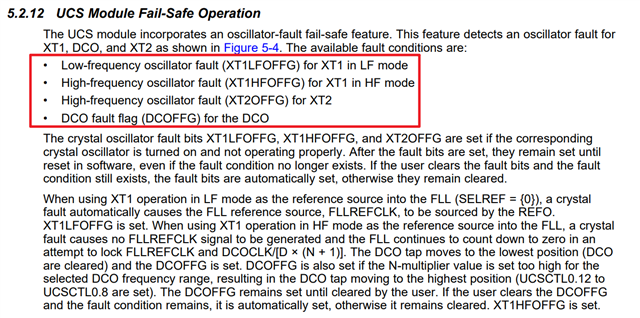

如题,设备正常运行一段时间,最近出现上电后程序不运行的现象,但通过重复上电可以临时解决。现在这种情况愈演愈烈,遂拆下检查故障。发现重复上电时,串口输出的就绪数据会出现乱码,偶尔也会恢复正常,如图:

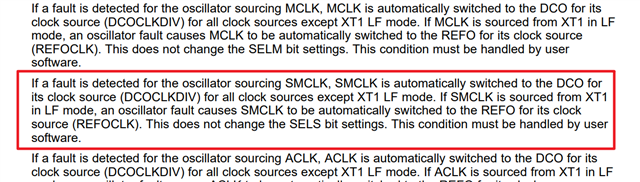

怀疑是晶振问题,更换晶振后现象依旧,配置SMCLK和MCLK输出引脚, 测量时钟输出发现以下几种现象:

1.MCLK每次都能正常测量为16M。

2.当串口出现乱码时,测量SMCLK发现测量不到,测量MCLK正常为16M,如视频所示。

3.上电后串口无数据,可以测量到SMCLK波形为8M,MCLK正常为16M。

以下为系统时钟配置代码

void init_clock(void)

{

P7DIR &=~P7DIR_0;

P7DIR|= P7DIR_1;

P7SEL|=P7SEL_0+P7SEL_1; // xt1in/xt1out引脚

UCSCTL6&=~XT1OFF; //XT1 ON ,外部晶振

UCSCTL6|=XTS; //高频模式,不选内部电容,

UCSCTL6&=~XT1BYPASS; //外部晶振

UCSCTL6&=~(XCAP0+XCAP1); //内部电容 2p469

UCSCTL6&=~XT1DRIVE_3; //01b8-16

UCSCTL4=0;

UCSCTL4|=SELA__REFOCLK; //ACLK选择内部32k

UCSCTL4|=SELS__XT1CLK; //SMCLK选择XT1=8M

UCSCTL4|=SELM__DCOCLKDIV; //MCLK选择DCOCLKDIV

__bis_SR_register(SCG0); //关闭FLL

UCSCTL0=0x0000; //自动修正

UCSCTL1|=DCORSEL_7; //DCO频率范围选择最大25M

UCSCTL2=FLLD_1; //DCOCLK不分频

UCSCTL2|=1; //FLLN=1,DCOCLK调制后为(1+1)*8M=16m

//UCSCTL3=SELREF__REFOCLK;//FLL参考 REFOCLK 不分频 (762+1)*32768

UCSCTL3=SELREF__XT1CLK; //FLL参考 选XT1 8m 不分频

__bic_SR_register(SCG0); //开启FLL DCOCLK=16M

__delay_cycles(782000);

do

{

UCSCTL7&=~(XT1LFOFFG+XT1HFOFFG+XT2OFFG+DCOFFG);

SFRIFG1&=~OFIFG;

Delay(250);

}

while(SFRIFG1&OFIFG);

PMMCTL0=0XA502;

SVSMHCTL=0X4602;

SVSMLCTL=0X4602;

// PMMRIE=0X1100;

}外部晶振XT1使用8M,该程序在其他芯片中运行正常,故障控制板更换芯片后也运行正常。该控制板尚未大规模使用,不知这种现象是否常见,作为使用者该如何规避这种情况。各位工程师是否遇到过类似情况,希望您能解答,谢谢。