Part Number: MSP430FR2433

About MSP430FR2433 ,I have a question about the difference between data in FRAM and RAM.Those are my code :

#pragma NOINIT(FRAM_write)

uint8_t FRAM_write[0x800]; //ADDRESS:0xC400

uint8_t RD_NG[8]={0xff,0xff,0xff,0xff,0xff,0xff,0xff,0xff}; //ADDRESS: RAM

For those data,I want to compare FRAM_write with RD_NG,

f_7100_DATA(); //for get FRAM_write

do{

if(strncmp(FRAM_write,RD_NG,8)!=0)

{

flag[0] = 0x37313030;

for(i=0;i<10;i++)

{

delay_ms(250);

P1OUT |= (BIT0); //P1.0 output low

delay_ms(250);

P1OUT &=~(BIT0); //P1.0 output low

}

}

else f_7100_DATA();

for(i=0;i<2;i++)

{

delay_ms(250);

P1OUT |= (BIT0); //P1.0 output low

delay_ms(250);

P1OUT &=~(BIT0); //P1.0 output low

}

}while(flag[0] != 0x37313030);

for(i=0;i<5;i++)

{

delay_ms(250);

P1OUT |= (BIT0); //P1.0 output low

delay_ms(250);

P1OUT &=~(BIT0); //P1.0 output low

}

delay_ms(50);

By the code ,I cannot get the result that the LED blinks 17 times.

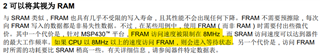

if I change FRAM_write[800] adresss: uint8_t FRAM_write[0x800]; //ADDRESS:0x2300 at RAM

I can get the result that the LED blinks 17 times.