Part Number: MSP430AFE253

Other Parts Discussed in Thread: TINA-TI

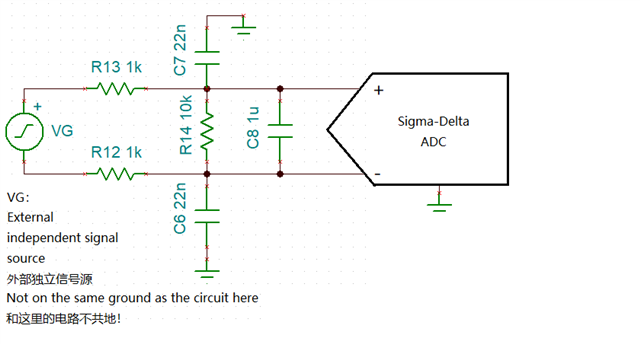

很多文档提到,使用 SD ADC 需要对其 差分输入 增加 抗混叠 RC 电路当作其前端电路,如下第一个图,实测在 MSP430AFE 的 SD24_A 上得到了 达到 0.03mV 的采集纹波(使用采样率 fS = fM / OSR = 60Hz,并加上软件实现的 10Hz 低通滤波) 。

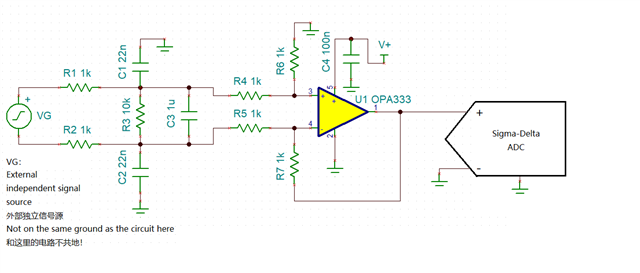

但是ADC具有一定输入阻抗,而前端电路存在的电阻会对采集精度造成影响,况且我的外部信号源也存在一定的输出阻抗(至少50KΩ),所以实测现在采集的电压量不准(计算是没有问题的),所以想在前面增加运放电路在缓冲下,如下两种,哪一种更优?

第二张图片,信号输入先经过抗混叠RC电路再经过差分运放电路再给到ADC,看起来可以,但是ADC输入的前面没有首先连接抗混叠RC电路是否会有问题?

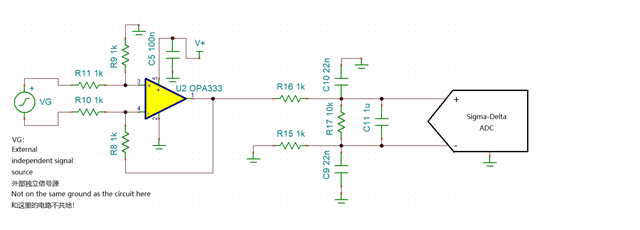

第三张图片,基于第二张图的疑惑,把抗混叠RC电路和运放电路交换位置,是否更好?但是有引入新的问题,我的输入信号是外部独立电路产生的输出信号,与这个ADC电路并不共地,这个输出信号直接连接差分运放是否可行?

Many documents mention that using a SD ADC requires adding an anti-aliasing RC circuit as its front-end for differential inputs, as shown in the first figure below. Actual tests on the MSP430AFE's SD24_A achieved a sampling ripple as low as 0.03mV (using a sampling rate fS = fM / OSR = 60Hz, along with a software-implemented 10Hz low-pass filter).

However, the ADC itself has a certain input impedance, and the resistors in the front-end circuit can affect sampling accuracy. Moreover, my external signal source also has some output impedance (at least 50KΩ). As a result, the currently measured voltage values are inaccurate (though the calculations are correct). Therefore, I'm considering adding an op-amp buffer circuit at the front. Between the two options below, which is better?

In the second figure, the signal first passes through the anti-aliasing RC circuit, then through a differential op-amp circuit before reaching the ADC. This seems feasible, but could there be an issue since the anti-aliasing RC circuit is not directly connected to the ADC input?

In the third figure, to address the concern above, the positions of the anti-aliasing RC circuit and the op-amp circuit are swapped. Would this be better? However, this introduces a new problem: my input signal is generated by an external independent circuit, which does not share a common ground with this ADC circuit. Is it acceptable to directly connect this output signal to the differential op-amp?