Part Number: MSPM0G3519

Dear Team,

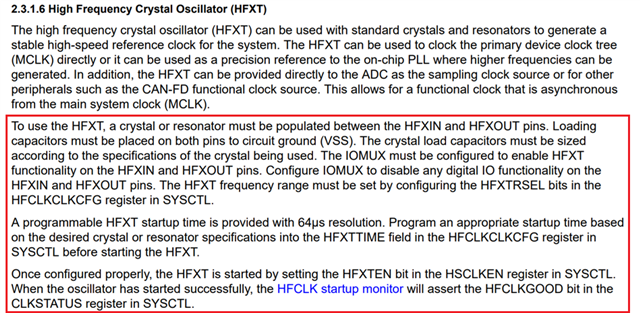

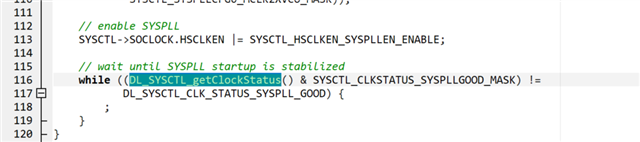

I am working on MSPM0G3519 controller(32 pin) and trying to start external crystal 16MHz, but it stuck at the below line:

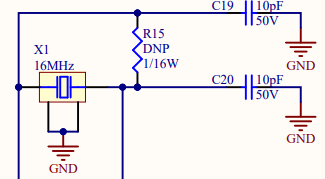

You can check the hardware design for crystal connection(HFIN connect at PTA5 and HFOUT connected at PTA6) :

Please check the attached configuration and help us to resolve the issue.

thank you.

/*

* Copyright (c) 2023, Texas Instruments Incorporated

* All rights reserved.

*

* Redistribution and use in source and binary forms, with or without

* modification, are permitted provided that the following conditions

* are met:

*

* * Redistributions of source code must retain the above copyright

* notice, this list of conditions and the following disclaimer.

*

* * Redistributions in binary form must reproduce the above copyright

* notice, this list of conditions and the following disclaimer in the

* documentation and/or other materials provided with the distribution.

*

* * Neither the name of Texas Instruments Incorporated nor the names of

* its contributors may be used to endorse or promote products derived

* from this software without specific prior written permission.

*

* THIS SOFTWARE IS PROVIDED BY THE COPYRIGHT HOLDERS AND CONTRIBUTORS "AS IS"

* AND ANY EXPRESS OR IMPLIED WARRANTIES, INCLUDING, BUT NOT LIMITED TO,

* THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR

* PURPOSE ARE DISCLAIMED. IN NO EVENT SHALL THE COPYRIGHT OWNER OR

* CONTRIBUTORS BE LIABLE FOR ANY DIRECT, INDIRECT, INCIDENTAL, SPECIAL,

* EXEMPLARY, OR CONSEQUENTIAL DAMAGES (INCLUDING, BUT NOT LIMITED TO,

* PROCUREMENT OF SUBSTITUTE GOODS OR SERVICES; LOSS OF USE, DATA, OR PROFITS;

* OR BUSINESS INTERRUPTION) HOWEVER CAUSED AND ON ANY THEORY OF LIABILITY,

* WHETHER IN CONTRACT, STRICT LIABILITY, OR TORT (INCLUDING NEGLIGENCE OR

* OTHERWISE) ARISING IN ANY WAY OUT OF THE USE OF THIS SOFTWARE,

* EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGE.

*/

/*

* ============ ti_msp_dl_config.c =============

* Configured MSPM0 DriverLib module definitions

*

* DO NOT EDIT - This file is generated for the MSPM0G351X

* by the SysConfig tool.

*/

#include "ti_msp_dl_config.h"

DL_TimerA_backupConfig gTIMER_10_MsBackup;

DL_TimerA_backupConfig gTIMER_1_MsBackup;

DL_SPI_backupConfig gSPI_1_EepromBackup;

/*

* ======== SYSCFG_DL_init ========

* Perform any initialization needed before using any board APIs

*/

SYSCONFIG_WEAK void SYSCFG_DL_init(void)

{

SYSCFG_DL_initPower();

SYSCFG_DL_GPIO_init();

/* Module-Specific Initializations*/

SYSCFG_DL_SYSCTL_init();

SYSCFG_DL_PWM_0_init();

SYSCFG_DL_TIMER_10_Ms_init();

SYSCFG_DL_TIMER_1_Ms_init();

SYSCFG_DL_LIN_0_init();

SYSCFG_DL_SPI_1_Eeprom_init();

SYSCFG_DL_WWDT1_init();

SYSCFG_DL_MCAN0_init();

SYSCFG_DL_SYSCTL_CLK_init();

/* Ensure backup structures have no valid state */

gTIMER_10_MsBackup.backupRdy = false;

gTIMER_1_MsBackup.backupRdy = false;

gSPI_1_EepromBackup.backupRdy = false;

}

/*

* User should take care to save and restore register configuration in application.

* See Retention Configuration section for more details.

*/

SYSCONFIG_WEAK bool SYSCFG_DL_saveConfiguration(void)

{

bool retStatus = true;

retStatus &= DL_TimerA_saveConfiguration(TIMER_10_Ms_INST, &gTIMER_10_MsBackup);

retStatus &= DL_TimerA_saveConfiguration(TIMER_1_Ms_INST, &gTIMER_1_MsBackup);

retStatus &= DL_SPI_saveConfiguration(SPI_1_Eeprom_INST, &gSPI_1_EepromBackup);

return retStatus;

}

SYSCONFIG_WEAK bool SYSCFG_DL_restoreConfiguration(void)

{

bool retStatus = true;

retStatus &= DL_TimerA_restoreConfiguration(TIMER_10_Ms_INST, &gTIMER_10_MsBackup, false);

retStatus &= DL_TimerA_restoreConfiguration(TIMER_1_Ms_INST, &gTIMER_1_MsBackup, false);

retStatus &= DL_SPI_restoreConfiguration(SPI_1_Eeprom_INST, &gSPI_1_EepromBackup);

return retStatus;

}

SYSCONFIG_WEAK void SYSCFG_DL_initPower(void)

{

DL_GPIO_reset(GPIOA);

DL_TimerG_reset(PWM_0_INST);

DL_TimerA_reset(TIMER_10_Ms_INST);

DL_TimerA_reset(TIMER_1_Ms_INST);

DL_UART_Extend_reset(LIN_0_INST);

DL_SPI_reset(SPI_1_Eeprom_INST);

DL_WWDT_reset(WWDT1_INST);

DL_MCAN_reset(MCAN0_INST);

DL_GPIO_enablePower(GPIOA);

DL_TimerG_enablePower(PWM_0_INST);

DL_TimerA_enablePower(TIMER_10_Ms_INST);

DL_TimerA_enablePower(TIMER_1_Ms_INST);

DL_UART_Extend_enablePower(LIN_0_INST);

DL_SPI_enablePower(SPI_1_Eeprom_INST);

DL_WWDT_enablePower(WWDT1_INST);

DL_MCAN_enablePower(MCAN0_INST);

delay_cycles(POWER_STARTUP_DELAY);

}

SYSCONFIG_WEAK void SYSCFG_DL_GPIO_init(void)

{

/* Configure GPIO/IOMUX for HFXT functionality */

DL_GPIO_initPeripheralAnalogFunction(GPIO_HFXIN_IOMUX);

DL_GPIO_initPeripheralAnalogFunction(GPIO_HFXOUT_IOMUX);

DL_GPIO_initPeripheralOutputFunction(GPIO_PWM_0_C0_IOMUX,GPIO_PWM_0_C0_IOMUX_FUNC);

DL_GPIO_enableOutput(GPIO_PWM_0_C0_PORT, GPIO_PWM_0_C0_PIN);

DL_GPIO_initPeripheralOutputFunction(

GPIO_LIN_0_IOMUX_TX, GPIO_LIN_0_IOMUX_TX_FUNC);

DL_GPIO_initPeripheralInputFunction(

GPIO_LIN_0_IOMUX_RX, GPIO_LIN_0_IOMUX_RX_FUNC);

DL_GPIO_initPeripheralOutputFunction(

GPIO_SPI_1_Eeprom_IOMUX_SCLK, GPIO_SPI_1_Eeprom_IOMUX_SCLK_FUNC);

DL_GPIO_initPeripheralOutputFunction(

GPIO_SPI_1_Eeprom_IOMUX_PICO, GPIO_SPI_1_Eeprom_IOMUX_PICO_FUNC);

DL_GPIO_initPeripheralInputFunction(

GPIO_SPI_1_Eeprom_IOMUX_POCI, GPIO_SPI_1_Eeprom_IOMUX_POCI_FUNC);

DL_GPIO_initDigitalOutput(GPIO_GRP_PTA_PIN_IND_LED6_IOMUX);

DL_GPIO_initDigitalOutput(GPIO_GRP_PTA_EEPROM_CS_PIN_IOMUX);

DL_GPIO_clearPins(GPIO_GRP_PTA_PORT, GPIO_GRP_PTA_PIN_IND_LED6_PIN);

DL_GPIO_setPins(GPIO_GRP_PTA_PORT, GPIO_GRP_PTA_EEPROM_CS_PIN_PIN);

DL_GPIO_enableOutput(GPIO_GRP_PTA_PORT, GPIO_GRP_PTA_PIN_IND_LED6_PIN |

GPIO_GRP_PTA_EEPROM_CS_PIN_PIN);

DL_GPIO_initPeripheralOutputFunction(

GPIO_MCAN0_IOMUX_CAN_TX, GPIO_MCAN0_IOMUX_CAN_TX_FUNC);

DL_GPIO_initPeripheralInputFunction(

GPIO_MCAN0_IOMUX_CAN_RX, GPIO_MCAN0_IOMUX_CAN_RX_FUNC);

}

static const DL_SYSCTL_SYSPLLConfig gSYSPLLConfig = {

.inputFreq = DL_SYSCTL_SYSPLL_INPUT_FREQ_16_32_MHZ,

.rDivClk2x = 1,

.rDivClk1 = 0,

.rDivClk0 = 0,

.enableCLK2x = DL_SYSCTL_SYSPLL_CLK2X_ENABLE,

.enableCLK1 = DL_SYSCTL_SYSPLL_CLK1_ENABLE,

.enableCLK0 = DL_SYSCTL_SYSPLL_CLK0_ENABLE,

.sysPLLMCLK = DL_SYSCTL_SYSPLL_MCLK_CLK2X,

.sysPLLRef = DL_SYSCTL_SYSPLL_REF_HFCLK,

.qDiv = 4,

.pDiv = DL_SYSCTL_SYSPLL_PDIV_1,

};

SYSCONFIG_WEAK void SYSCFG_DL_SYSCTL_init(void)

{

//Low Power Mode is configured to be SLEEP0

DL_SYSCTL_setBORThreshold(DL_SYSCTL_BOR_THRESHOLD_LEVEL_0);

DL_SYSCTL_setFlashWaitState(DL_SYSCTL_FLASH_WAIT_STATE_2);

DL_SYSCTL_setSYSOSCFreq(DL_SYSCTL_SYSOSC_FREQ_BASE);

/* Set default configuration */

DL_SYSCTL_disableHFXT();

DL_SYSCTL_disableSYSPLL();

DL_SYSCTL_setHFCLKSourceHFXTParams(DL_SYSCTL_HFXT_RANGE_8_16_MHZ, 10, false);

DL_SYSCTL_configSYSPLL((DL_SYSCTL_SYSPLLConfig *) &gSYSPLLConfig);

DL_SYSCTL_setULPCLKDivider(DL_SYSCTL_ULPCLK_DIV_1);

DL_SYSCTL_setMCLKSource(SYSOSC, HSCLK, DL_SYSCTL_HSCLK_SOURCE_SYSPLL);

DL_SYSCTL_setMCLKDivider(DL_SYSCTL_MCLK_DIVIDER_DISABLE);

}

SYSCONFIG_WEAK void SYSCFG_DL_SYSCTL_CLK_init(void) {

while ((DL_SYSCTL_getClockStatus() & (DL_SYSCTL_CLK_STATUS_SYSPLL_GOOD

| DL_SYSCTL_CLK_STATUS_HFCLK_GOOD

| DL_SYSCTL_CLK_STATUS_HSCLK_GOOD

| DL_SYSCTL_CLK_STATUS_LFOSC_GOOD))

!= (DL_SYSCTL_CLK_STATUS_SYSPLL_GOOD

| DL_SYSCTL_CLK_STATUS_HFCLK_GOOD

| DL_SYSCTL_CLK_STATUS_HSCLK_GOOD

| DL_SYSCTL_CLK_STATUS_LFOSC_GOOD))

{

/* Ensure that clocks are in default POR configuration before initialization.

* Additionally once LFXT is enabled, the internal LFOSC is disabled, and cannot

* be re-enabled other than by executing a BOOTRST. */

;

}

}

/*

* Timer clock configuration to be sourced by / 4 (20000000 Hz)

* timerClkFreq = (timerClkSrc / (timerClkDivRatio * (timerClkPrescale + 1)))

* 20000000 Hz = 20000000 Hz / (4 * (0 + 1))

*/

static const DL_TimerG_ClockConfig gPWM_0ClockConfig = {

.clockSel = DL_TIMER_CLOCK_BUSCLK,

.divideRatio = DL_TIMER_CLOCK_DIVIDE_4,

.prescale = 0U

};

static const DL_TimerG_PWMConfig gPWM_0Config = {

.pwmMode = DL_TIMER_PWM_MODE_EDGE_ALIGN_UP,

.period = 1000,

.isTimerWithFourCC = false,

.startTimer = DL_TIMER_STOP,

};

SYSCONFIG_WEAK void SYSCFG_DL_PWM_0_init(void) {

DL_TimerG_setClockConfig(

PWM_0_INST, (DL_TimerG_ClockConfig *) &gPWM_0ClockConfig);

DL_TimerG_initPWMMode(

PWM_0_INST, (DL_TimerG_PWMConfig *) &gPWM_0Config);

// Set Counter control to the smallest CC index being used

DL_TimerG_setCounterControl(PWM_0_INST,DL_TIMER_CZC_CCCTL0_ZCOND,DL_TIMER_CAC_CCCTL0_ACOND,DL_TIMER_CLC_CCCTL0_LCOND);

DL_TimerG_setCaptureCompareOutCtl(PWM_0_INST, DL_TIMER_CC_OCTL_INIT_VAL_LOW,

DL_TIMER_CC_OCTL_INV_OUT_DISABLED, DL_TIMER_CC_OCTL_SRC_FUNCVAL,

DL_TIMERG_CAPTURE_COMPARE_0_INDEX);

DL_TimerG_setCaptCompUpdateMethod(PWM_0_INST, DL_TIMER_CC_UPDATE_METHOD_IMMEDIATE, DL_TIMERG_CAPTURE_COMPARE_0_INDEX);

DL_TimerG_setCaptureCompareValue(PWM_0_INST, 0, DL_TIMER_CC_0_INDEX);

DL_TimerG_enableClock(PWM_0_INST);

DL_TimerG_setCCPDirection(PWM_0_INST , DL_TIMER_CC0_OUTPUT );

}

/*

* Timer clock configuration to be sourced by BUSCLK / (10000000 Hz)

* timerClkFreq = (timerClkSrc / (timerClkDivRatio * (timerClkPrescale + 1)))

* 10000000 Hz = 10000000 Hz / (8 * (0 + 1))

*/

static const DL_TimerA_ClockConfig gTIMER_10_MsClockConfig = {

.clockSel = DL_TIMER_CLOCK_BUSCLK,

.divideRatio = DL_TIMER_CLOCK_DIVIDE_8,

.prescale = 0U,

};

/*

* Timer load value (where the counter starts from) is calculated as (timerPeriod * timerClockFreq) - 1

* TIMER_10_Ms_INST_LOAD_VALUE = (5ms * 10000000 Hz) - 1

*/

static const DL_TimerA_TimerConfig gTIMER_10_MsTimerConfig = {

.period = TIMER_10_Ms_INST_LOAD_VALUE,

.timerMode = DL_TIMER_TIMER_MODE_PERIODIC,

.startTimer = DL_TIMER_STOP,

};

SYSCONFIG_WEAK void SYSCFG_DL_TIMER_10_Ms_init(void) {

DL_TimerA_setClockConfig(TIMER_10_Ms_INST,

(DL_TimerA_ClockConfig *) &gTIMER_10_MsClockConfig);

DL_TimerA_initTimerMode(TIMER_10_Ms_INST,

(DL_TimerA_TimerConfig *) &gTIMER_10_MsTimerConfig);

DL_TimerA_enableInterrupt(TIMER_10_Ms_INST , DL_TIMERA_INTERRUPT_REPC_EVENT);

DL_TimerA_setRepeatCounter(TIMER_10_Ms_INST, TIMER_10_Ms_REPEAT_COUNT_2);

DL_TimerA_enableClock(TIMER_10_Ms_INST);

}

/*

* Timer clock configuration to be sourced by BUSCLK / (10000000 Hz)

* timerClkFreq = (timerClkSrc / (timerClkDivRatio * (timerClkPrescale + 1)))

* 10000000 Hz = 10000000 Hz / (8 * (0 + 1))

*/

static const DL_TimerA_ClockConfig gTIMER_1_MsClockConfig = {

.clockSel = DL_TIMER_CLOCK_BUSCLK,

.divideRatio = DL_TIMER_CLOCK_DIVIDE_8,

.prescale = 0U,

};

/*

* Timer load value (where the counter starts from) is calculated as (timerPeriod * timerClockFreq) - 1

* TIMER_1_Ms_INST_LOAD_VALUE = (1 ms * 10000000 Hz) - 1

*/

static const DL_TimerA_TimerConfig gTIMER_1_MsTimerConfig = {

.period = TIMER_1_Ms_INST_LOAD_VALUE,

.timerMode = DL_TIMER_TIMER_MODE_PERIODIC,

.startTimer = DL_TIMER_STOP,

};

SYSCONFIG_WEAK void SYSCFG_DL_TIMER_1_Ms_init(void) {

DL_TimerA_setClockConfig(TIMER_1_Ms_INST,

(DL_TimerA_ClockConfig *) &gTIMER_1_MsClockConfig);

DL_TimerA_initTimerMode(TIMER_1_Ms_INST,

(DL_TimerA_TimerConfig *) &gTIMER_1_MsTimerConfig);

DL_TimerA_enableInterrupt(TIMER_1_Ms_INST , DL_TIMERA_INTERRUPT_ZERO_EVENT);

DL_TimerA_enableClock(TIMER_1_Ms_INST);

}

static const DL_UART_Extend_ClockConfig gLIN_0ClockConfig = {

.clockSel = DL_UART_EXTEND_CLOCK_BUSCLK,

.divideRatio = DL_UART_EXTEND_CLOCK_DIVIDE_RATIO_2

};

static const DL_UART_Extend_Config gLIN_0Config = {

.mode = DL_UART_EXTEND_MODE_NORMAL,

.direction = DL_UART_EXTEND_DIRECTION_TX_RX,

.flowControl = DL_UART_EXTEND_FLOW_CONTROL_NONE,

.parity = DL_UART_EXTEND_PARITY_NONE,

.wordLength = DL_UART_EXTEND_WORD_LENGTH_8_BITS,

.stopBits = DL_UART_EXTEND_STOP_BITS_ONE

};

SYSCONFIG_WEAK void SYSCFG_DL_LIN_0_init(void)

{

DL_UART_Extend_setClockConfig(LIN_0_INST, (DL_UART_Extend_ClockConfig *) &gLIN_0ClockConfig);

DL_UART_Extend_init(LIN_0_INST, (DL_UART_Extend_Config *) &gLIN_0Config);

/*

* Configure baud rate by setting oversampling and baud rate divisors.

* Target baud rate: 19200

* Actual baud rate: 19200.77

*/

DL_UART_Extend_setOversampling(LIN_0_INST, DL_UART_OVERSAMPLING_RATE_16X);

DL_UART_Extend_setBaudRateDivisor(LIN_0_INST, LIN_0_IBRD_40_MHZ_19200_BAUD, LIN_0_FBRD_40_MHZ_19200_BAUD);

/* Configure Interrupts */

DL_UART_Extend_enableInterrupt(LIN_0_INST,

DL_UART_EXTEND_INTERRUPT_BREAK_ERROR |

DL_UART_EXTEND_INTERRUPT_LINC0_MATCH |

DL_UART_EXTEND_INTERRUPT_LIN_COUNTER_OVERFLOW |

DL_UART_EXTEND_INTERRUPT_LIN_FALLING_EDGE |

DL_UART_EXTEND_INTERRUPT_RXD_POS_EDGE);

/* Configure LIN settings */

DL_UART_Extend_enableLINCounter(LIN_0_INST);

DL_UART_Extend_setLINCounterValue(LIN_0_INST, 0);

DL_UART_Extend_enableLINCounterCompareMatch(LIN_0_INST);

DL_UART_Extend_setLINCounterCompareValue(LIN_0_INST, LIN_0_COUNTER_COMPARE_VALUE);

DL_UART_Extend_enableLINCountWhileLow(LIN_0_INST);

DL_UART_Extend_enableLINCounterClearOnFallingEdge(LIN_0_INST);

DL_UART_Extend_enable(LIN_0_INST);

}

static const DL_SPI_Config gSPI_1_Eeprom_config = {

.mode = DL_SPI_MODE_CONTROLLER,

.frameFormat = DL_SPI_FRAME_FORMAT_MOTO3_POL0_PHA0,

.parity = DL_SPI_PARITY_NONE,

.dataSize = DL_SPI_DATA_SIZE_8,

.bitOrder = DL_SPI_BIT_ORDER_MSB_FIRST,

};

static const DL_SPI_ClockConfig gSPI_1_Eeprom_clockConfig = {

.clockSel = DL_SPI_CLOCK_BUSCLK,

.divideRatio = DL_SPI_CLOCK_DIVIDE_RATIO_1

};

SYSCONFIG_WEAK void SYSCFG_DL_SPI_1_Eeprom_init(void) {

DL_SPI_setClockConfig(SPI_1_Eeprom_INST, (DL_SPI_ClockConfig *) &gSPI_1_Eeprom_clockConfig);

DL_SPI_init(SPI_1_Eeprom_INST, (DL_SPI_Config *) &gSPI_1_Eeprom_config);

/* Configure Controller mode */

/*

* Set the bit rate clock divider to generate the serial output clock

* outputBitRate = (spiInputClock) / ((1 + SCR) * 2)

* 4000000 = (80000000)/((1 + 9) * 2)

*/

DL_SPI_setBitRateSerialClockDivider(SPI_1_Eeprom_INST, 9);

/* Set RX and TX FIFO threshold levels */

DL_SPI_setFIFOThreshold(SPI_1_Eeprom_INST, DL_SPI_RX_FIFO_LEVEL_1_2_FULL, DL_SPI_TX_FIFO_LEVEL_1_2_EMPTY);

/* Enable module */

DL_SPI_enable(SPI_1_Eeprom_INST);

}

SYSCONFIG_WEAK void SYSCFG_DL_WWDT1_init(void)

{

/*

* Initialize WWDT1 in Watchdog mode with following settings

* Watchdog Source Clock = (LFCLK Freq) / (WWDT Clock Divider)

* = 32768Hz / 2 = 16.38 kHz

* Watchdog Period = (WWDT Clock Divider) ∗ (WWDT Period Count) / 32768Hz

* = 2 * 2^12 / 32768Hz = 250.00 ms

* Window0 Closed Period = (WWDT Period) * (Window0 Closed Percent)

* = 250.00 ms * 0% = 0.00 s

* Window1 Closed Period = (WWDT Period) * (Window1 Closed Percent)

* = 250.00 ms * 0% = 0.00 s

*/

DL_WWDT_initWatchdogMode(WWDT1_INST, DL_WWDT_CLOCK_DIVIDE_2,

DL_WWDT_TIMER_PERIOD_12_BITS, DL_WWDT_STOP_IN_SLEEP,

DL_WWDT_WINDOW_PERIOD_0, DL_WWDT_WINDOW_PERIOD_0);

/* Set Window0 as active window */

DL_WWDT_setActiveWindow(WWDT1_INST, DL_WWDT_WINDOW0);

}

static const DL_MCAN_ClockConfig gMCAN0ClockConf = {

.clockSel = DL_MCAN_FCLK_HFCLK,

.divider = DL_MCAN_FCLK_DIV_1,

};

static const DL_MCAN_InitParams gMCAN0InitParams= {

/* Initialize MCAN Init parameters. */

.fdMode = true,

.brsEnable = true,

.txpEnable = false,

.efbi = false,

.pxhddisable = false,

.darEnable = false,

.wkupReqEnable = true,

.autoWkupEnable = true,

.emulationEnable = true,

.tdcEnable = true,

.wdcPreload = 255,

/* Transmitter Delay Compensation parameters. */

.tdcConfig.tdcf = 10,

.tdcConfig.tdco = 6,

};

static const DL_MCAN_ConfigParams gMCAN0ConfigParams={

/* Initialize MCAN Config parameters. */

.monEnable = false,

.asmEnable = false,

.tsPrescalar = 15,

.tsSelect = 0,

.timeoutSelect = DL_MCAN_TIMEOUT_SELECT_CONT,

.timeoutPreload = 65535,

.timeoutCntEnable = false,

.filterConfig.rrfs = true,

.filterConfig.rrfe = true,

.filterConfig.anfe = 1,

.filterConfig.anfs = 1,

};

static const DL_MCAN_MsgRAMConfigParams gMCAN0MsgRAMConfigParams ={

/* Standard ID Filter List Start Address. */

.flssa = MCAN0_INST_MCAN_STD_ID_FILT_START_ADDR,

/* List Size: Standard ID. */

.lss = MCAN0_INST_MCAN_STD_ID_FILTER_NUM,

/* Extended ID Filter List Start Address. */

.flesa = MCAN0_INST_MCAN_EXT_ID_FILT_START_ADDR,

/* List Size: Extended ID. */

.lse = MCAN0_INST_MCAN_EXT_ID_FILTER_NUM,

/* Tx Buffers Start Address. */

.txStartAddr = MCAN0_INST_MCAN_TX_BUFF_START_ADDR,

/* Number of Dedicated Transmit Buffers. */

.txBufNum = MCAN0_INST_MCAN_TX_BUFF_SIZE,

.txFIFOSize = 10,

/* Tx Buffer Element Size. */

.txBufMode = 0,

.txBufElemSize = DL_MCAN_ELEM_SIZE_64BYTES,

/* Tx Event FIFO Start Address. */

.txEventFIFOStartAddr = MCAN0_INST_MCAN_TX_EVENT_START_ADDR,

/* Event FIFO Size. */

.txEventFIFOSize = MCAN0_INST_MCAN_TX_EVENT_SIZE,

/* Level for Tx Event FIFO watermark interrupt. */

.txEventFIFOWaterMark = 0,

/* Rx FIFO0 Start Address. */

.rxFIFO0startAddr = MCAN0_INST_MCAN_FIFO_0_START_ADDR,

/* Number of Rx FIFO elements. */

.rxFIFO0size = MCAN0_INST_MCAN_FIFO_0_NUM,

/* Rx FIFO0 Watermark. */

.rxFIFO0waterMark = 0,

.rxFIFO0OpMode = 0,

/* Rx FIFO1 Start Address. */

.rxFIFO1startAddr = MCAN0_INST_MCAN_FIFO_1_START_ADDR,

/* Number of Rx FIFO elements. */

.rxFIFO1size = MCAN0_INST_MCAN_FIFO_1_NUM,

/* Level for Rx FIFO 1 watermark interrupt. */

.rxFIFO1waterMark = 0,

/* FIFO blocking mode. */

.rxFIFO1OpMode = 0,

/* Rx Buffer Start Address. */

.rxBufStartAddr = MCAN0_INST_MCAN_RX_BUFF_START_ADDR,

/* Rx Buffer Element Size. */

.rxBufElemSize = DL_MCAN_ELEM_SIZE_64BYTES,

/* Rx FIFO0 Element Size. */

.rxFIFO0ElemSize = DL_MCAN_ELEM_SIZE_64BYTES,

/* Rx FIFO1 Element Size. */

.rxFIFO1ElemSize = DL_MCAN_ELEM_SIZE_64BYTES,

};

static const DL_MCAN_StdMsgIDFilterElement gMCAN0StdFiltelem = {

.sfec = 0x7,

.sft = 0x1,

.sfid1 = 272,

.sfid2 = 0,

};

static const DL_MCAN_BitTimingParams gMCAN0BitTimes = {

/* Arbitration Baud Rate Pre-scaler. */

.nomRatePrescalar = 0,

/* Arbitration Time segment before sample point. */

.nomTimeSeg1 = 26,

/* Arbitration Time segment after sample point. */

.nomTimeSeg2 = 3,

/* Arbitration (Re)Synchronization Jump Width Range. */

.nomSynchJumpWidth = 3,

/* Data Baud Rate Pre-scaler. */

.dataRatePrescalar = 0,

/* Data Time segment before sample point. */

.dataTimeSeg1 = 5,

/* Data Time segment after sample point. */

.dataTimeSeg2 = 0,

/* Data (Re)Synchronization Jump Width. */

.dataSynchJumpWidth = 0,

};

SYSCONFIG_WEAK void SYSCFG_DL_MCAN0_init(void) {

DL_MCAN_RevisionId revid_MCAN0;

DL_MCAN_enableModuleClock(MCAN0_INST);

DL_MCAN_setClockConfig(MCAN0_INST, (DL_MCAN_ClockConfig *) &gMCAN0ClockConf);

/* Get MCANSS Revision ID. */

DL_MCAN_getRevisionId(MCAN0_INST, &revid_MCAN0);

/* Wait for Memory initialization to be completed. */

while(false == DL_MCAN_isMemInitDone(MCAN0_INST));

/* Put MCAN in SW initialization mode. */

DL_MCAN_setOpMode(MCAN0_INST, DL_MCAN_OPERATION_MODE_SW_INIT);

/* Wait till MCAN is not initialized. */

while (DL_MCAN_OPERATION_MODE_SW_INIT != DL_MCAN_getOpMode(MCAN0_INST));

/* Initialize MCAN module. */

DL_MCAN_init(MCAN0_INST, (DL_MCAN_InitParams *) &gMCAN0InitParams);

/* Configure MCAN module. */

DL_MCAN_config(MCAN0_INST, (DL_MCAN_ConfigParams*) &gMCAN0ConfigParams);

/* Configure Bit timings. */

DL_MCAN_setBitTime(MCAN0_INST, (DL_MCAN_BitTimingParams*) &gMCAN0BitTimes);

/* Configure Message RAM Sections */

DL_MCAN_msgRAMConfig(MCAN0_INST, (DL_MCAN_MsgRAMConfigParams*) &gMCAN0MsgRAMConfigParams);

/* Configure Standard ID filter element */

DL_MCAN_addStdMsgIDFilter(MCAN0_INST, 0U, (DL_MCAN_StdMsgIDFilterElement *) &gMCAN0StdFiltelem);

/* Set Extended ID Mask. */

DL_MCAN_setExtIDAndMask(MCAN0_INST, MCAN0_INST_MCAN_EXT_ID_AND_MASK );

/* Loopback mode */

/* Take MCAN out of the SW initialization mode */

DL_MCAN_setOpMode(MCAN0_INST, DL_MCAN_OPERATION_MODE_NORMAL);

while (DL_MCAN_OPERATION_MODE_NORMAL != DL_MCAN_getOpMode(MCAN0_INST));

/* Enable MCAN mopdule Interrupts */

DL_MCAN_enableIntr(MCAN0_INST, MCAN0_INST_MCAN_INTERRUPTS, 1U);

DL_MCAN_selectIntrLine(MCAN0_INST, DL_MCAN_INTERRUPT_BO|DL_MCAN_INTERRUPT_DRX|DL_MCAN_INTERRUPT_TC, DL_MCAN_INTR_LINE_NUM_0);

DL_MCAN_enableIntrLine(MCAN0_INST, DL_MCAN_INTR_LINE_NUM_0, 1U);

/* Enable MSPM0 MCAN interrupt */

DL_MCAN_clearInterruptStatus(MCAN0_INST,(DL_MCAN_MSP_INTERRUPT_LINE0));

DL_MCAN_enableInterrupt(MCAN0_INST,(DL_MCAN_MSP_INTERRUPT_LINE0));

}