Part Number: SYSCONFIG

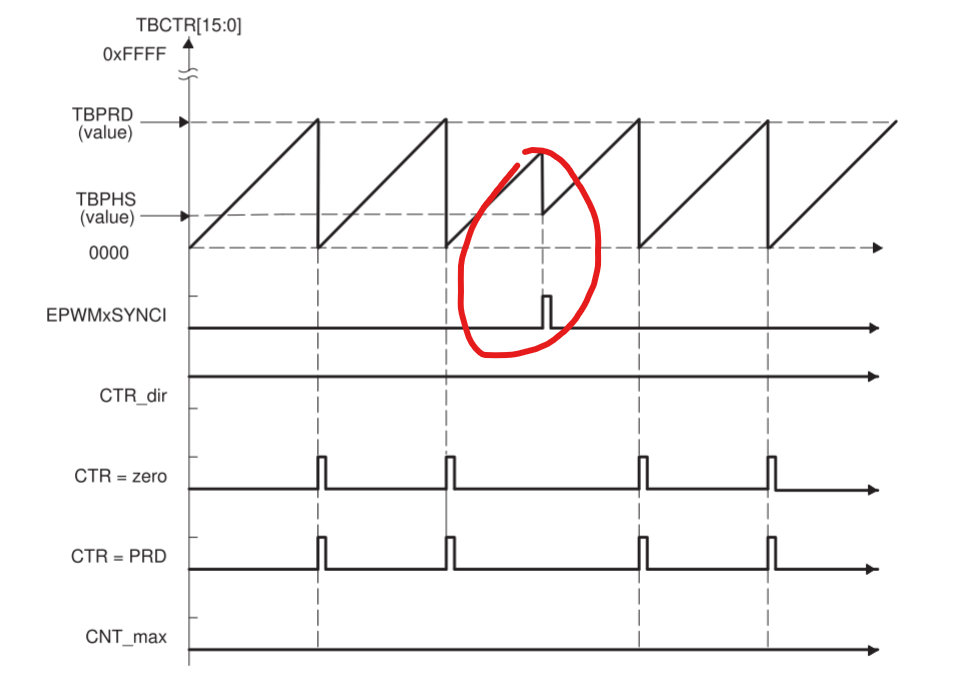

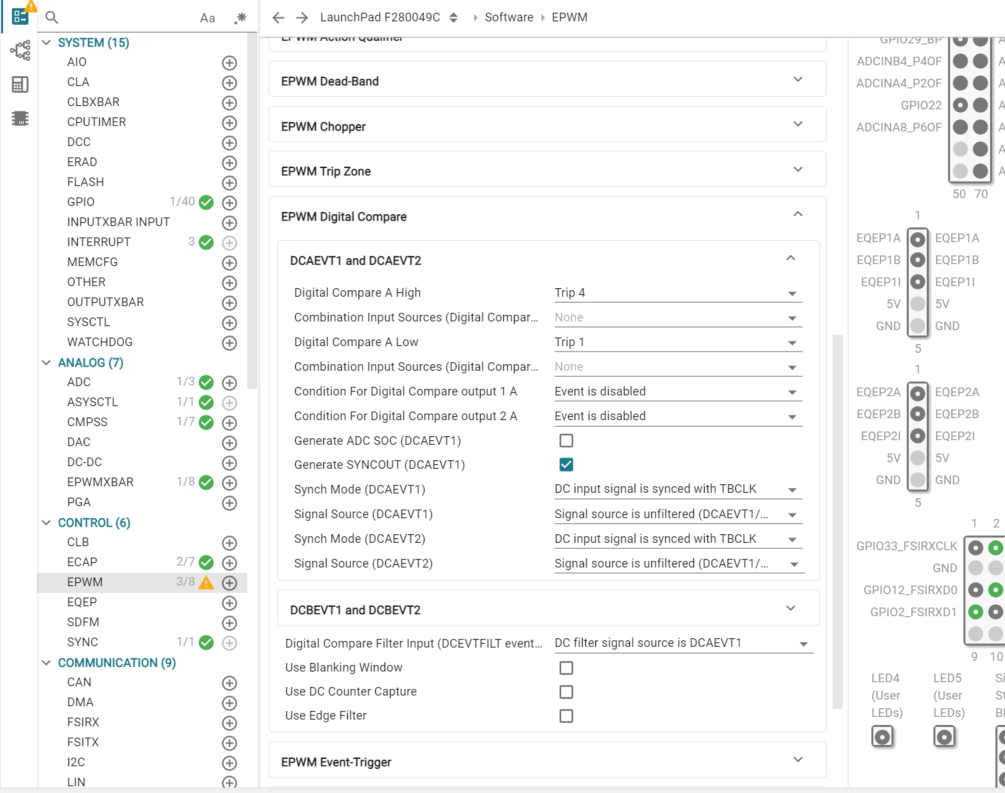

when the inductor current is greater than 0, the CMPSS pin inputs a high level (1); when the inductor current is less than 0, the CMPSS pin inputs a low level (0). The ePWM1 counter is refreshed when the CMPSS comparison value transitions from 1 to 0.

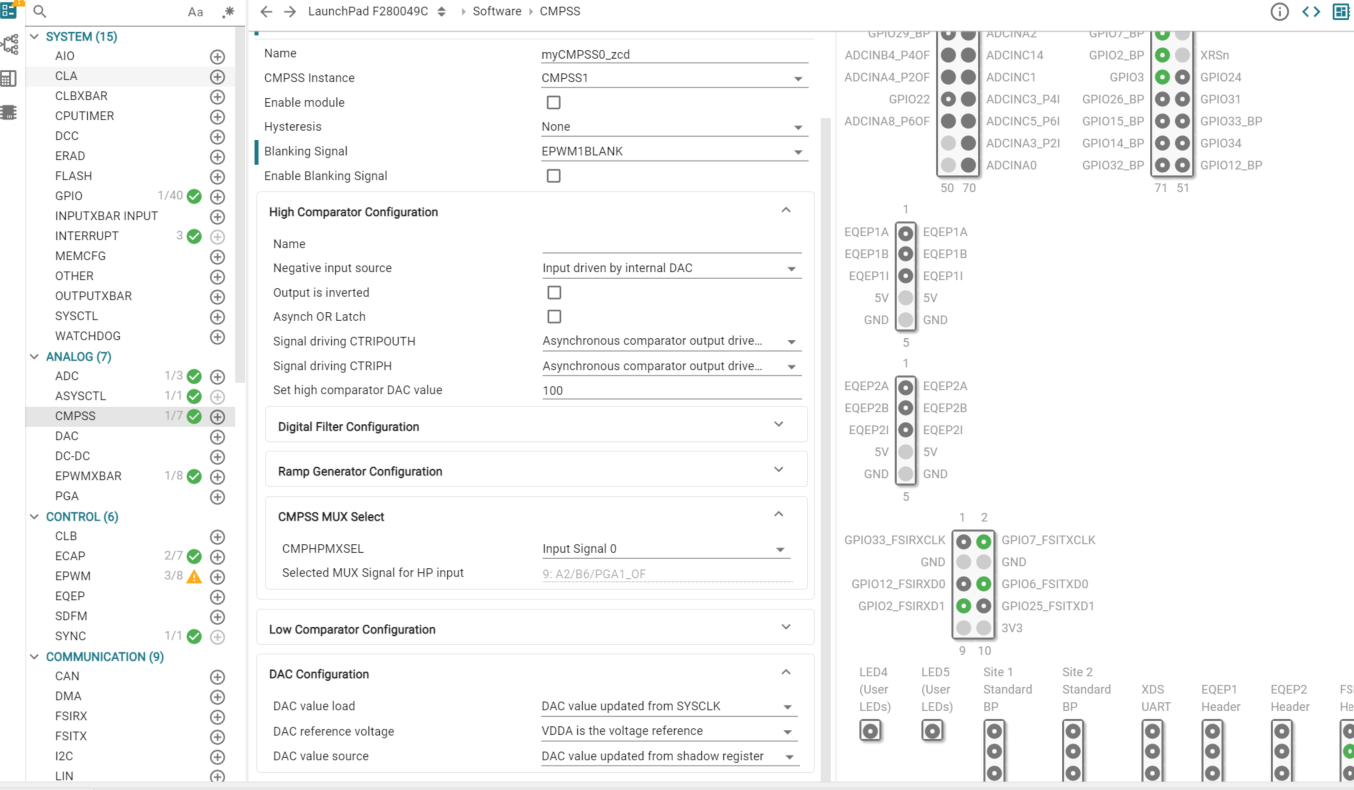

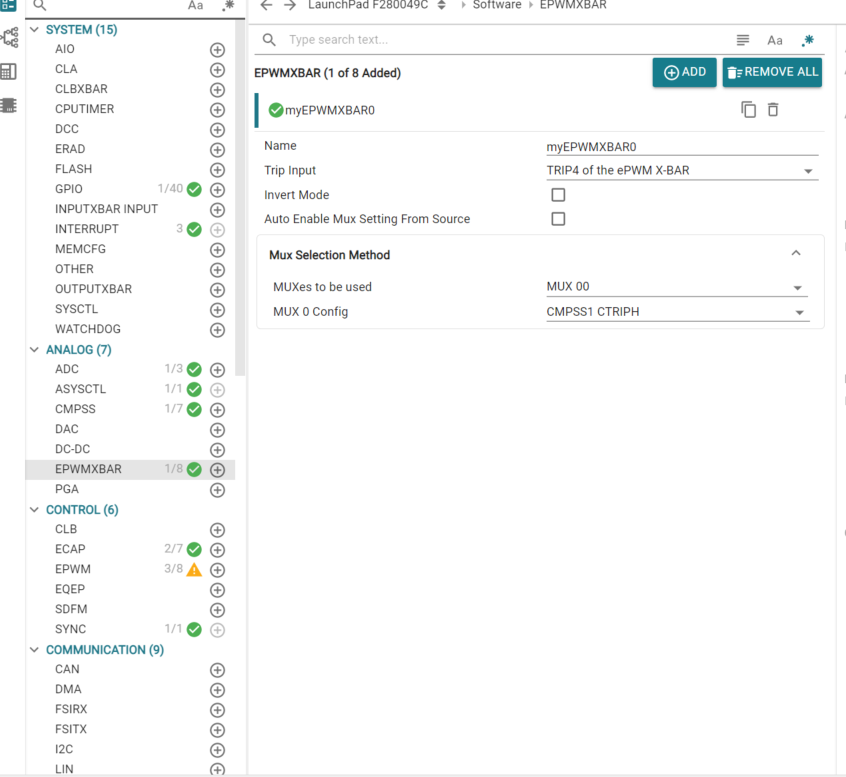

Could you help check if the configuration here is correct?

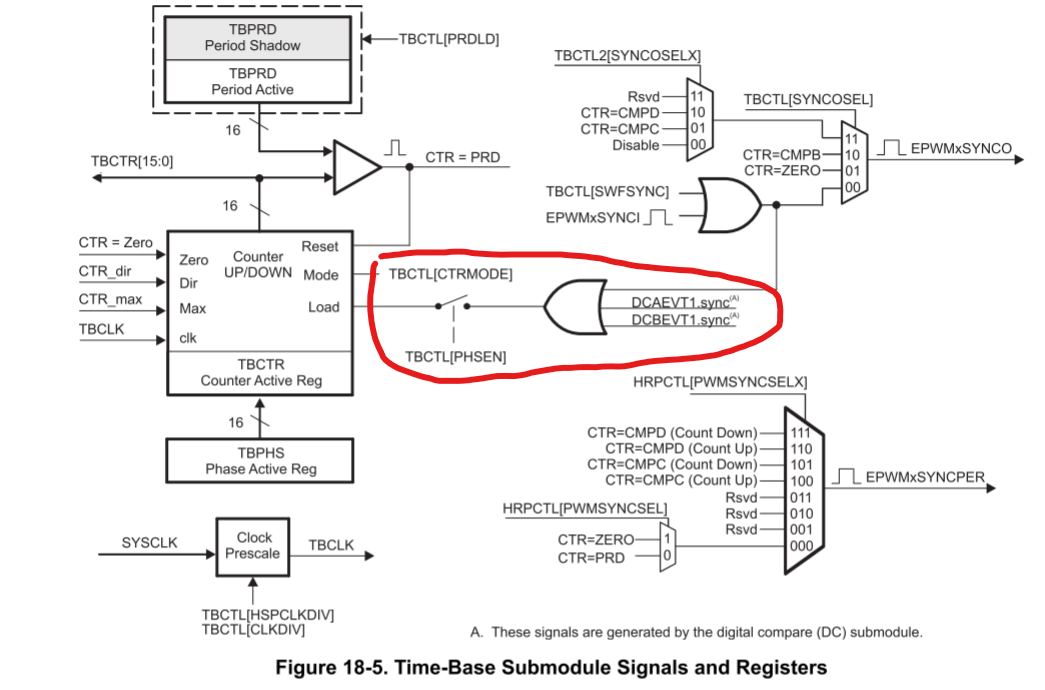

My approach is: CMPSS → ePWM X-Bar → ePWM1. When ZCD is generated, DCAEVT1.sync is triggered; configure TBPHS=0 to reset the counter.

But does this TBPHS need to be filled in manually?

/*

* Copyright (c) 2020 Texas Instruments Incorporated - http://www.ti.com

* All rights reserved.

*

* Redistribution and use in source and binary forms, with or without

* modification, are permitted provided that the following conditions

* are met:

*

* * Redistributions of source code must retain the above copyright

* notice, this list of conditions and the following disclaimer.

*

* * Redistributions in binary form must reproduce the above copyright

* notice, this list of conditions and the following disclaimer in the

* documentation and/or other materials provided with the distribution.

*

* * Neither the name of Texas Instruments Incorporated nor the names of

* its contributors may be used to endorse or promote products derived

* from this software without specific prior written permission.

*

* THIS SOFTWARE IS PROVIDED BY THE COPYRIGHT HOLDERS AND CONTRIBUTORS "AS IS"

* AND ANY EXPRESS OR IMPLIED WARRANTIES, INCLUDING, BUT NOT LIMITED TO,

* THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR

* PURPOSE ARE DISCLAIMED. IN NO EVENT SHALL THE COPYRIGHT OWNER OR

* CONTRIBUTORS BE LIABLE FOR ANY DIRECT, INDIRECT, INCIDENTAL, SPECIAL,

* EXEMPLARY, OR CONSEQUENTIAL DAMAGES (INCLUDING, BUT NOT LIMITED TO,

* PROCUREMENT OF SUBSTITUTE GOODS OR SERVICES; LOSS OF USE, DATA, OR PROFITS;

* OR BUSINESS INTERRUPTION) HOWEVER CAUSED AND ON ANY THEORY OF LIABILITY,

* WHETHER IN CONTRACT, STRICT LIABILITY, OR TORT (INCLUDING NEGLIGENCE OR

* OTHERWISE) ARISING IN ANY WAY OUT OF THE USE OF THIS SOFTWARE,

* EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGE.

*

*/

#include "board.h"

//*****************************************************************************

//

// Board Configurations

// Initializes the rest of the modules.

// Call this function in your application if you wish to do all module

// initialization.

// If you wish to not use some of the initializations, instead of the

// Board_init use the individual Module_inits

//

//*****************************************************************************

void Board_init()

{

EALLOW;

PinMux_init();

SYNC_init();

ASYSCTL_init();

ADC_init();

CMPSS_init();

ECAP_init();

EPWM_init();

EPWMXBAR_init();

GPIO_init();

INTERRUPT_init();

EDIS;

}

//*****************************************************************************

//

// PINMUX Configurations

//

//*****************************************************************************

void PinMux_init()

{

//

// PinMux for modules assigned to CPU1

//

//

// EPWM2 -> myEPWM0 Pinmux

//

GPIO_setPinConfig(myEPWM0_EPWMA_PIN_CONFIG);

GPIO_setPadConfig(myEPWM0_EPWMA_GPIO, GPIO_PIN_TYPE_STD);

GPIO_setQualificationMode(myEPWM0_EPWMA_GPIO, GPIO_QUAL_SYNC);

GPIO_setPinConfig(myEPWM0_EPWMB_PIN_CONFIG);

GPIO_setPadConfig(myEPWM0_EPWMB_GPIO, GPIO_PIN_TYPE_STD);

GPIO_setQualificationMode(myEPWM0_EPWMB_GPIO, GPIO_QUAL_SYNC);

//

// EPWM1 -> myEPWM1 Pinmux

//

GPIO_setPinConfig(myEPWM1_EPWMA_PIN_CONFIG);

GPIO_setPadConfig(myEPWM1_EPWMA_GPIO, GPIO_PIN_TYPE_STD);

GPIO_setQualificationMode(myEPWM1_EPWMA_GPIO, GPIO_QUAL_SYNC);

GPIO_setPinConfig(myEPWM1_EPWMB_PIN_CONFIG);

GPIO_setPadConfig(myEPWM1_EPWMB_GPIO, GPIO_PIN_TYPE_STD);

GPIO_setQualificationMode(myEPWM1_EPWMB_GPIO, GPIO_QUAL_SYNC);

//

// EPWM4 -> myEPWM2 Pinmux

//

GPIO_setPinConfig(myEPWM2_EPWMA_PIN_CONFIG);

GPIO_setPadConfig(myEPWM2_EPWMA_GPIO, GPIO_PIN_TYPE_STD);

GPIO_setQualificationMode(myEPWM2_EPWMA_GPIO, GPIO_QUAL_SYNC);

GPIO_setPinConfig(myEPWM2_EPWMB_PIN_CONFIG);

GPIO_setPadConfig(myEPWM2_EPWMB_GPIO, GPIO_PIN_TYPE_STD);

GPIO_setQualificationMode(myEPWM2_EPWMB_GPIO, GPIO_QUAL_SYNC);

// GPIO58 -> myGPIO_Relay Pinmux

GPIO_setPinConfig(GPIO_58_GPIO58);

}

//*****************************************************************************

//

// ADC Configurations

//

//*****************************************************************************

void ADC_init(){

myADCA_init();

}

void myADCA_init(){

//

// ADC Initialization: Write ADC configurations and power up the ADC

//

// Set the analog voltage reference selection and ADC module's offset trims.

// This function sets the analog voltage reference to internal (with the reference voltage of 1.65V or 2.5V) or external for ADC

// which is same as ASysCtl APIs.

//

ADC_setVREF(myADCA_BASE, ADC_REFERENCE_EXTERNAL, ADC_REFERENCE_2_5V);

//

// Configures the analog-to-digital converter module prescaler.

//

ADC_setPrescaler(myADCA_BASE, ADC_CLK_DIV_2_0);

//

// Sets the timing of the end-of-conversion pulse

//

ADC_setInterruptPulseMode(myADCA_BASE, ADC_PULSE_END_OF_ACQ_WIN);

//

// Sets the timing of early interrupt generation.

//

ADC_setInterruptCycleOffset(myADCA_BASE, 0U);

//

// Powers up the analog-to-digital converter core.

//

ADC_enableConverter(myADCA_BASE);

//

// Delay for 1ms to allow ADC time to power up

//

DEVICE_DELAY_US(500);

//

// SOC Configuration: Setup ADC EPWM channel and trigger settings

//

// Disables SOC burst mode.

//

ADC_disableBurstMode(myADCA_BASE);

//

// Sets the priority mode of the SOCs.

//

ADC_setSOCPriority(myADCA_BASE, ADC_PRI_ALL_ROUND_ROBIN);

//

// Start of Conversion 0 Configuration

//

//

// Configures a start-of-conversion (SOC) in the ADC and its interrupt SOC trigger.

// SOC number : 0

// Trigger : ADC_TRIGGER_EPWM2_SOCA

// Channel : ADC_CH_ADCIN0

// Sample Window : 10 SYSCLK cycles

// Interrupt Trigger: ADC_INT_SOC_TRIGGER_NONE

//

ADC_setupSOC(myADCA_BASE, ADC_SOC_NUMBER0, ADC_TRIGGER_EPWM2_SOCA, ADC_CH_ADCIN0, 10U);

ADC_setInterruptSOCTrigger(myADCA_BASE, ADC_SOC_NUMBER0, ADC_INT_SOC_TRIGGER_NONE);

//

// Start of Conversion 1 Configuration

//

//

// Configures a start-of-conversion (SOC) in the ADC and its interrupt SOC trigger.

// SOC number : 1

// Trigger : ADC_TRIGGER_EPWM2_SOCA

// Channel : ADC_CH_ADCIN1

// Sample Window : 10 SYSCLK cycles

// Interrupt Trigger: ADC_INT_SOC_TRIGGER_NONE

//

ADC_setupSOC(myADCA_BASE, ADC_SOC_NUMBER1, ADC_TRIGGER_EPWM2_SOCA, ADC_CH_ADCIN1, 10U);

ADC_setInterruptSOCTrigger(myADCA_BASE, ADC_SOC_NUMBER1, ADC_INT_SOC_TRIGGER_NONE);

}

//*****************************************************************************

//

// ASYSCTL Configurations

//

//*****************************************************************************

void ASYSCTL_init(){

//

// asysctl initialization

//

// Disables the temperature sensor output to the ADC.

//

ASysCtl_disableTemperatureSensor();

//

// Set the analog voltage reference selection to external.

//

ASysCtl_setAnalogReferenceExternal( ASYSCTL_VREFHIA | ASYSCTL_VREFHIB | ASYSCTL_VREFHIC );

}

//*****************************************************************************

//

// CMPSS Configurations

//

//*****************************************************************************

void CMPSS_init(){

myCMPSS0_zcd_init();

}

void myCMPSS0_zcd_init(){

//

// Select the value for CMP1HPMXSEL.

//

ASysCtl_selectCMPHPMux(ASYSCTL_CMPHPMUX_SELECT_1,0U);

//

// Select the value for CMP1LPMXSEL.

//

ASysCtl_selectCMPLPMux(ASYSCTL_CMPLPMUX_SELECT_1,0U);

//

// Sets the configuration for the high comparator.

//

CMPSS_configHighComparator(myCMPSS0_zcd_BASE,(CMPSS_INSRC_DAC));

//

// Sets the configuration for the low comparator.

//

CMPSS_configLowComparator(myCMPSS0_zcd_BASE,(CMPSS_INSRC_DAC));

//

// Sets the configuration for the internal comparator DACs.

//

CMPSS_configDAC(myCMPSS0_zcd_BASE,(CMPSS_DACVAL_SYSCLK | CMPSS_DACREF_VDDA | CMPSS_DACSRC_SHDW));

//

// Sets the value of the internal DAC of the high comparator.

//

CMPSS_setDACValueHigh(myCMPSS0_zcd_BASE,100U);

//

// Sets the value of the internal DAC of the low comparator.

//

CMPSS_setDACValueLow(myCMPSS0_zcd_BASE,0U);

//

// Configures the digital filter of the high comparator.

//

CMPSS_configFilterHigh(myCMPSS0_zcd_BASE, 0U, 1U, 1U);

//

// Configures the digital filter of the low comparator.

//

CMPSS_configFilterLow(myCMPSS0_zcd_BASE, 0U, 1U, 1U);

//

// Sets the output signal configuration for the high comparator.

//

CMPSS_configOutputsHigh(myCMPSS0_zcd_BASE,(CMPSS_TRIPOUT_ASYNC_COMP | CMPSS_TRIP_ASYNC_COMP));

//

// Sets the output signal configuration for the low comparator.

//

CMPSS_configOutputsLow(myCMPSS0_zcd_BASE,(CMPSS_TRIPOUT_ASYNC_COMP | CMPSS_TRIP_ASYNC_COMP));

//

// Sets the comparator hysteresis settings.

//

CMPSS_setHysteresis(myCMPSS0_zcd_BASE,0U);

//

// Configures the comparator subsystem's ramp generator.

//

CMPSS_configRamp(myCMPSS0_zcd_BASE,0U,0U,0U,1U,true);

//

// Disables reset of HIGH comparator digital filter output latch on PWMSYNC

//

CMPSS_disableLatchResetOnPWMSYNCHigh(myCMPSS0_zcd_BASE);

//

// Disables reset of LOW comparator digital filter output latch on PWMSYNC

//

CMPSS_disableLatchResetOnPWMSYNCLow(myCMPSS0_zcd_BASE);

//

// Sets the ePWM module blanking signal that holds trip in reset.

//

CMPSS_configBlanking(myCMPSS0_zcd_BASE,1U);

//

// Disables an ePWM blanking signal from holding trip in reset.

//

CMPSS_disableBlanking(myCMPSS0_zcd_BASE);

//

// Configures whether or not the digital filter latches are reset by PWMSYNC

//

CMPSS_configLatchOnPWMSYNC(myCMPSS0_zcd_BASE,false,false);

//

// Disables the CMPSS module.

//

CMPSS_disableModule(myCMPSS0_zcd_BASE);

//

// Delay for CMPSS DAC to power up.

//

DEVICE_DELAY_US(500);

}

//*****************************************************************************

//

// ECAP Configurations

//

//*****************************************************************************

void ECAP_init(){

myECAP0_init();

myECAP1_init();

}

void myECAP0_init(){

//

// Disable ,clear all capture flags and interrupts

//

ECAP_disableInterrupt(myECAP0_BASE,

(ECAP_ISR_SOURCE_CAPTURE_EVENT_1 |

ECAP_ISR_SOURCE_CAPTURE_EVENT_2 |

ECAP_ISR_SOURCE_CAPTURE_EVENT_3 |

ECAP_ISR_SOURCE_CAPTURE_EVENT_4 |

ECAP_ISR_SOURCE_COUNTER_OVERFLOW |

ECAP_ISR_SOURCE_COUNTER_PERIOD |

ECAP_ISR_SOURCE_COUNTER_COMPARE));

ECAP_clearInterrupt(myECAP0_BASE,

(ECAP_ISR_SOURCE_CAPTURE_EVENT_1 |

ECAP_ISR_SOURCE_CAPTURE_EVENT_2 |

ECAP_ISR_SOURCE_CAPTURE_EVENT_3 |

ECAP_ISR_SOURCE_CAPTURE_EVENT_4 |

ECAP_ISR_SOURCE_COUNTER_OVERFLOW |

ECAP_ISR_SOURCE_COUNTER_PERIOD |

ECAP_ISR_SOURCE_COUNTER_COMPARE));

//

// Disables time stamp capture.

//

ECAP_disableTimeStampCapture(myECAP0_BASE);

//

// Stops Time stamp counter.

//

ECAP_stopCounter(myECAP0_BASE);

//

// Sets eCAP in Capture mode.

//

ECAP_enableCaptureMode(myECAP0_BASE);

//

// Sets the capture mode.

//

ECAP_setCaptureMode(myECAP0_BASE,ECAP_CONTINUOUS_CAPTURE_MODE,ECAP_EVENT_4);

//

// Sets the Capture event prescaler.

//

ECAP_setEventPrescaler(myECAP0_BASE, 0U);

//

// Sets the Capture event polarity.

//

ECAP_setEventPolarity(myECAP0_BASE,ECAP_EVENT_1,ECAP_EVNT_RISING_EDGE);

ECAP_setEventPolarity(myECAP0_BASE,ECAP_EVENT_2,ECAP_EVNT_FALLING_EDGE);

ECAP_setEventPolarity(myECAP0_BASE,ECAP_EVENT_3,ECAP_EVNT_RISING_EDGE);

ECAP_setEventPolarity(myECAP0_BASE,ECAP_EVENT_4,ECAP_EVNT_FALLING_EDGE);

//

// Configure counter reset on events

//

ECAP_disableCounterResetOnEvent(myECAP0_BASE,ECAP_EVENT_1);

ECAP_disableCounterResetOnEvent(myECAP0_BASE,ECAP_EVENT_2);

ECAP_disableCounterResetOnEvent(myECAP0_BASE,ECAP_EVENT_3);

ECAP_disableCounterResetOnEvent(myECAP0_BASE,ECAP_EVENT_4);

//

// Select eCAP input.

//

ECAP_selectECAPInput(myECAP0_BASE,ECAP_INPUT_INPUTXBAR6);

//

// Sets a phase shift value count.

//

ECAP_setPhaseShiftCount(myECAP0_BASE,0U);

//

// Disable counter loading with phase shift value.

//

ECAP_disableLoadCounter(myECAP0_BASE);

//

// Configures Sync out signal mode.

//

ECAP_setSyncOutMode(myECAP0_BASE,ECAP_SYNC_OUT_SYNCI);

//

// Configures emulation mode.

//

ECAP_setEmulationMode(myECAP0_BASE,ECAP_EMULATION_STOP);

//

// Starts Time stamp counter for myECAP0.

//

ECAP_startCounter(myECAP0_BASE);

//

// Enables time stamp capture for myECAP0.

//

ECAP_enableTimeStampCapture(myECAP0_BASE);

//

// Re-arms the eCAP module for myECAP0.

//

ECAP_reArm(myECAP0_BASE);

}

void myECAP1_init(){

//

// Disable ,clear all capture flags and interrupts

//

ECAP_disableInterrupt(myECAP1_BASE,

(ECAP_ISR_SOURCE_CAPTURE_EVENT_1 |

ECAP_ISR_SOURCE_CAPTURE_EVENT_2 |

ECAP_ISR_SOURCE_CAPTURE_EVENT_3 |

ECAP_ISR_SOURCE_CAPTURE_EVENT_4 |

ECAP_ISR_SOURCE_COUNTER_OVERFLOW |

ECAP_ISR_SOURCE_COUNTER_PERIOD |

ECAP_ISR_SOURCE_COUNTER_COMPARE));

ECAP_clearInterrupt(myECAP1_BASE,

(ECAP_ISR_SOURCE_CAPTURE_EVENT_1 |

ECAP_ISR_SOURCE_CAPTURE_EVENT_2 |

ECAP_ISR_SOURCE_CAPTURE_EVENT_3 |

ECAP_ISR_SOURCE_CAPTURE_EVENT_4 |

ECAP_ISR_SOURCE_COUNTER_OVERFLOW |

ECAP_ISR_SOURCE_COUNTER_PERIOD |

ECAP_ISR_SOURCE_COUNTER_COMPARE));

//

// Disables time stamp capture.

//

ECAP_disableTimeStampCapture(myECAP1_BASE);

//

// Stops Time stamp counter.

//

ECAP_stopCounter(myECAP1_BASE);

//

// Sets eCAP in Capture mode.

//

ECAP_enableCaptureMode(myECAP1_BASE);

//

// Sets the capture mode.

//

ECAP_setCaptureMode(myECAP1_BASE,ECAP_CONTINUOUS_CAPTURE_MODE,ECAP_EVENT_4);

//

// Sets the Capture event prescaler.

//

ECAP_setEventPrescaler(myECAP1_BASE, 0U);

//

// Sets the Capture event polarity.

//

ECAP_setEventPolarity(myECAP1_BASE,ECAP_EVENT_1,ECAP_EVNT_RISING_EDGE);

ECAP_setEventPolarity(myECAP1_BASE,ECAP_EVENT_2,ECAP_EVNT_FALLING_EDGE);

ECAP_setEventPolarity(myECAP1_BASE,ECAP_EVENT_3,ECAP_EVNT_RISING_EDGE);

ECAP_setEventPolarity(myECAP1_BASE,ECAP_EVENT_4,ECAP_EVNT_FALLING_EDGE);

//

// Configure counter reset on events

//

ECAP_disableCounterResetOnEvent(myECAP1_BASE,ECAP_EVENT_1);

ECAP_disableCounterResetOnEvent(myECAP1_BASE,ECAP_EVENT_2);

ECAP_disableCounterResetOnEvent(myECAP1_BASE,ECAP_EVENT_3);

ECAP_disableCounterResetOnEvent(myECAP1_BASE,ECAP_EVENT_4);

//

// Select eCAP input.

//

ECAP_selectECAPInput(myECAP1_BASE,ECAP_INPUT_INPUTXBAR7);

//

// Sets a phase shift value count.

//

ECAP_setPhaseShiftCount(myECAP1_BASE,0U);

//

// Disable counter loading with phase shift value.

//

ECAP_disableLoadCounter(myECAP1_BASE);

//

// Configures Sync out signal mode.

//

ECAP_setSyncOutMode(myECAP1_BASE,ECAP_SYNC_OUT_SYNCI);

//

// Configures emulation mode.

//

ECAP_setEmulationMode(myECAP1_BASE,ECAP_EMULATION_STOP);

//

// Starts Time stamp counter for myECAP1.

//

ECAP_startCounter(myECAP1_BASE);

//

// Enables time stamp capture for myECAP1.

//

ECAP_enableTimeStampCapture(myECAP1_BASE);

//

// Re-arms the eCAP module for myECAP1.

//

ECAP_reArm(myECAP1_BASE);

}

//*****************************************************************************

//

// EPWM Configurations

//

//*****************************************************************************

void EPWM_init(){

EPWM_setClockPrescaler(myEPWM0_BASE, EPWM_CLOCK_DIVIDER_8, EPWM_HSCLOCK_DIVIDER_10);

EPWM_setTimeBasePeriod(myEPWM0_BASE, 12500);

EPWM_setTimeBaseCounter(myEPWM0_BASE, 0);

EPWM_setTimeBaseCounterMode(myEPWM0_BASE, EPWM_COUNTER_MODE_UP_DOWN);

EPWM_disablePhaseShiftLoad(myEPWM0_BASE);

EPWM_setPhaseShift(myEPWM0_BASE, 0);

EPWM_setCounterCompareValue(myEPWM0_BASE, EPWM_COUNTER_COMPARE_A, 6250);

EPWM_enableGlobalLoadRegisters(myEPWM0_BASE, EPWM_GL_REGISTER_CMPA_CMPAHR);

EPWM_setCounterCompareShadowLoadMode(myEPWM0_BASE, EPWM_COUNTER_COMPARE_A, EPWM_COMP_LOAD_ON_CNTR_ZERO);

EPWM_setCounterCompareValue(myEPWM0_BASE, EPWM_COUNTER_COMPARE_B, 0);

EPWM_setCounterCompareShadowLoadMode(myEPWM0_BASE, EPWM_COUNTER_COMPARE_B, EPWM_COMP_LOAD_ON_CNTR_ZERO);

EPWM_disableActionQualifierShadowLoadMode(myEPWM0_BASE, EPWM_ACTION_QUALIFIER_A);

EPWM_setActionQualifierShadowLoadMode(myEPWM0_BASE, EPWM_ACTION_QUALIFIER_A, EPWM_AQ_LOAD_ON_CNTR_ZERO);

EPWM_setActionQualifierAction(myEPWM0_BASE, EPWM_AQ_OUTPUT_A, EPWM_AQ_OUTPUT_NO_CHANGE, EPWM_AQ_OUTPUT_ON_TIMEBASE_ZERO);

EPWM_setActionQualifierAction(myEPWM0_BASE, EPWM_AQ_OUTPUT_A, EPWM_AQ_OUTPUT_NO_CHANGE, EPWM_AQ_OUTPUT_ON_TIMEBASE_PERIOD);

EPWM_setActionQualifierAction(myEPWM0_BASE, EPWM_AQ_OUTPUT_A, EPWM_AQ_OUTPUT_HIGH, EPWM_AQ_OUTPUT_ON_TIMEBASE_UP_CMPA);

EPWM_setActionQualifierAction(myEPWM0_BASE, EPWM_AQ_OUTPUT_A, EPWM_AQ_OUTPUT_LOW, EPWM_AQ_OUTPUT_ON_TIMEBASE_DOWN_CMPA);

EPWM_setActionQualifierAction(myEPWM0_BASE, EPWM_AQ_OUTPUT_A, EPWM_AQ_OUTPUT_NO_CHANGE, EPWM_AQ_OUTPUT_ON_TIMEBASE_UP_CMPB);

EPWM_setActionQualifierAction(myEPWM0_BASE, EPWM_AQ_OUTPUT_A, EPWM_AQ_OUTPUT_NO_CHANGE, EPWM_AQ_OUTPUT_ON_TIMEBASE_DOWN_CMPB);

EPWM_disableActionQualifierShadowLoadMode(myEPWM0_BASE, EPWM_ACTION_QUALIFIER_B);

EPWM_setActionQualifierShadowLoadMode(myEPWM0_BASE, EPWM_ACTION_QUALIFIER_B, EPWM_AQ_LOAD_ON_CNTR_ZERO);

EPWM_setActionQualifierAction(myEPWM0_BASE, EPWM_AQ_OUTPUT_B, EPWM_AQ_OUTPUT_NO_CHANGE, EPWM_AQ_OUTPUT_ON_TIMEBASE_ZERO);

EPWM_setActionQualifierAction(myEPWM0_BASE, EPWM_AQ_OUTPUT_B, EPWM_AQ_OUTPUT_NO_CHANGE, EPWM_AQ_OUTPUT_ON_TIMEBASE_PERIOD);

EPWM_setActionQualifierAction(myEPWM0_BASE, EPWM_AQ_OUTPUT_B, EPWM_AQ_OUTPUT_NO_CHANGE, EPWM_AQ_OUTPUT_ON_TIMEBASE_UP_CMPA);

EPWM_setActionQualifierAction(myEPWM0_BASE, EPWM_AQ_OUTPUT_B, EPWM_AQ_OUTPUT_NO_CHANGE, EPWM_AQ_OUTPUT_ON_TIMEBASE_DOWN_CMPA);

EPWM_setActionQualifierAction(myEPWM0_BASE, EPWM_AQ_OUTPUT_B, EPWM_AQ_OUTPUT_NO_CHANGE, EPWM_AQ_OUTPUT_ON_TIMEBASE_UP_CMPB);

EPWM_setActionQualifierAction(myEPWM0_BASE, EPWM_AQ_OUTPUT_B, EPWM_AQ_OUTPUT_NO_CHANGE, EPWM_AQ_OUTPUT_ON_TIMEBASE_DOWN_CMPB);

EPWM_setDeadBandDelayPolarity(myEPWM0_BASE, EPWM_DB_FED, EPWM_DB_POLARITY_ACTIVE_LOW);

EPWM_setDeadBandDelayMode(myEPWM0_BASE, EPWM_DB_RED, true);

EPWM_setRisingEdgeDelayCountShadowLoadMode(myEPWM0_BASE, EPWM_RED_LOAD_ON_CNTR_ZERO);

EPWM_disableRisingEdgeDelayCountShadowLoadMode(myEPWM0_BASE);

EPWM_setRisingEdgeDelayCount(myEPWM0_BASE, 2);

EPWM_setDeadBandDelayMode(myEPWM0_BASE, EPWM_DB_FED, true);

EPWM_setFallingEdgeDelayCountShadowLoadMode(myEPWM0_BASE, EPWM_FED_LOAD_ON_CNTR_ZERO);

EPWM_disableFallingEdgeDelayCountShadowLoadMode(myEPWM0_BASE);

EPWM_setFallingEdgeDelayCount(myEPWM0_BASE, 2);

EPWM_enableADCTrigger(myEPWM0_BASE, EPWM_SOC_A);

EPWM_setADCTriggerSource(myEPWM0_BASE, EPWM_SOC_A, EPWM_SOC_TBCTR_ZERO);

EPWM_setADCTriggerEventPrescale(myEPWM0_BASE, EPWM_SOC_A, 1);

EPWM_setClockPrescaler(myEPWM1_BASE, EPWM_CLOCK_DIVIDER_1, EPWM_HSCLOCK_DIVIDER_1);

EPWM_setTimeBasePeriod(myEPWM1_BASE, 999);

EPWM_enableGlobalLoadRegisters(myEPWM1_BASE, EPWM_GL_REGISTER_TBPRD_TBPRDHR);

EPWM_setTimeBaseCounter(myEPWM1_BASE, 0);

EPWM_setTimeBaseCounterMode(myEPWM1_BASE, EPWM_COUNTER_MODE_UP);

EPWM_disablePhaseShiftLoad(myEPWM1_BASE);

EPWM_setPhaseShift(myEPWM1_BASE, 0);

EPWM_setSyncOutPulseMode(myEPWM1_BASE, EPWM_SYNC_OUT_PULSE_ON_COUNTER_ZERO);

EPWM_setCounterCompareValue(myEPWM1_BASE, EPWM_COUNTER_COMPARE_A, 0);

EPWM_setCounterCompareShadowLoadMode(myEPWM1_BASE, EPWM_COUNTER_COMPARE_A, EPWM_COMP_LOAD_ON_CNTR_ZERO);

EPWM_setCounterCompareValue(myEPWM1_BASE, EPWM_COUNTER_COMPARE_B, 492);

EPWM_setCounterCompareShadowLoadMode(myEPWM1_BASE, EPWM_COUNTER_COMPARE_B, EPWM_COMP_LOAD_ON_CNTR_ZERO);

EPWM_disableActionQualifierShadowLoadMode(myEPWM1_BASE, EPWM_ACTION_QUALIFIER_A);

EPWM_setActionQualifierShadowLoadMode(myEPWM1_BASE, EPWM_ACTION_QUALIFIER_A, EPWM_AQ_LOAD_ON_CNTR_ZERO);

EPWM_setActionQualifierAction(myEPWM1_BASE, EPWM_AQ_OUTPUT_A, EPWM_AQ_OUTPUT_NO_CHANGE, EPWM_AQ_OUTPUT_ON_TIMEBASE_ZERO);

EPWM_setActionQualifierAction(myEPWM1_BASE, EPWM_AQ_OUTPUT_A, EPWM_AQ_OUTPUT_NO_CHANGE, EPWM_AQ_OUTPUT_ON_TIMEBASE_PERIOD);

EPWM_setActionQualifierAction(myEPWM1_BASE, EPWM_AQ_OUTPUT_A, EPWM_AQ_OUTPUT_HIGH, EPWM_AQ_OUTPUT_ON_TIMEBASE_UP_CMPA);

EPWM_setActionQualifierAction(myEPWM1_BASE, EPWM_AQ_OUTPUT_A, EPWM_AQ_OUTPUT_NO_CHANGE, EPWM_AQ_OUTPUT_ON_TIMEBASE_DOWN_CMPA);

EPWM_setActionQualifierAction(myEPWM1_BASE, EPWM_AQ_OUTPUT_A, EPWM_AQ_OUTPUT_LOW, EPWM_AQ_OUTPUT_ON_TIMEBASE_UP_CMPB);

EPWM_setActionQualifierAction(myEPWM1_BASE, EPWM_AQ_OUTPUT_A, EPWM_AQ_OUTPUT_NO_CHANGE, EPWM_AQ_OUTPUT_ON_TIMEBASE_DOWN_CMPB);

EPWM_disableActionQualifierShadowLoadMode(myEPWM1_BASE, EPWM_ACTION_QUALIFIER_B);

EPWM_setActionQualifierShadowLoadMode(myEPWM1_BASE, EPWM_ACTION_QUALIFIER_B, EPWM_AQ_LOAD_ON_CNTR_ZERO);

EPWM_setActionQualifierAction(myEPWM1_BASE, EPWM_AQ_OUTPUT_B, EPWM_AQ_OUTPUT_NO_CHANGE, EPWM_AQ_OUTPUT_ON_TIMEBASE_ZERO);

EPWM_setActionQualifierAction(myEPWM1_BASE, EPWM_AQ_OUTPUT_B, EPWM_AQ_OUTPUT_NO_CHANGE, EPWM_AQ_OUTPUT_ON_TIMEBASE_PERIOD);

EPWM_setActionQualifierAction(myEPWM1_BASE, EPWM_AQ_OUTPUT_B, EPWM_AQ_OUTPUT_NO_CHANGE, EPWM_AQ_OUTPUT_ON_TIMEBASE_UP_CMPA);

EPWM_setActionQualifierAction(myEPWM1_BASE, EPWM_AQ_OUTPUT_B, EPWM_AQ_OUTPUT_NO_CHANGE, EPWM_AQ_OUTPUT_ON_TIMEBASE_DOWN_CMPA);

EPWM_setActionQualifierAction(myEPWM1_BASE, EPWM_AQ_OUTPUT_B, EPWM_AQ_OUTPUT_NO_CHANGE, EPWM_AQ_OUTPUT_ON_TIMEBASE_UP_CMPB);

EPWM_setActionQualifierAction(myEPWM1_BASE, EPWM_AQ_OUTPUT_B, EPWM_AQ_OUTPUT_NO_CHANGE, EPWM_AQ_OUTPUT_ON_TIMEBASE_DOWN_CMPB);

EPWM_setDeadBandDelayPolarity(myEPWM1_BASE, EPWM_DB_FED, EPWM_DB_POLARITY_ACTIVE_LOW);

EPWM_setDeadBandDelayMode(myEPWM1_BASE, EPWM_DB_RED, true);

EPWM_setRisingEdgeDelayCountShadowLoadMode(myEPWM1_BASE, EPWM_RED_LOAD_ON_CNTR_ZERO);

EPWM_disableRisingEdgeDelayCountShadowLoadMode(myEPWM1_BASE);

EPWM_setRisingEdgeDelayCount(myEPWM1_BASE, 20);

EPWM_setDeadBandDelayMode(myEPWM1_BASE, EPWM_DB_FED, true);

EPWM_setFallingEdgeDelayCountShadowLoadMode(myEPWM1_BASE, EPWM_FED_LOAD_ON_CNTR_ZERO);

EPWM_disableFallingEdgeDelayCountShadowLoadMode(myEPWM1_BASE);

EPWM_setFallingEdgeDelayCount(myEPWM1_BASE, 20);

EPWM_enableGlobalLoadRegisters(myEPWM1_BASE, EPWM_GL_REGISTER_DBRED_DBREDHR);

EPWM_enableGlobalLoadRegisters(myEPWM1_BASE, EPWM_GL_REGISTER_DBFED_DBFEDHR);

EPWM_selectDigitalCompareTripInput(myEPWM1_BASE, EPWM_DC_TRIP_TRIPIN4, EPWM_DC_TYPE_DCAH);

EPWM_enableDigitalCompareSyncEvent(myEPWM1_BASE, EPWM_DC_MODULE_A);

EPWM_setClockPrescaler(myEPWM2_BASE, EPWM_CLOCK_DIVIDER_1, EPWM_HSCLOCK_DIVIDER_2);

EPWM_setTimeBasePeriod(myEPWM2_BASE, 999);

EPWM_setTimeBaseCounter(myEPWM2_BASE, 0);

EPWM_setTimeBaseCounterMode(myEPWM2_BASE, EPWM_COUNTER_MODE_UP);

EPWM_enablePhaseShiftLoad(myEPWM2_BASE);

EPWM_setPhaseShift(myEPWM2_BASE, 0);

EPWM_setSyncOutPulseMode(myEPWM2_BASE, EPWM_SYNC_OUT_PULSE_ON_EPWMxSYNCIN);

EPWM_setCounterCompareValue(myEPWM2_BASE, EPWM_COUNTER_COMPARE_A, 0);

EPWM_setCounterCompareShadowLoadMode(myEPWM2_BASE, EPWM_COUNTER_COMPARE_A, EPWM_COMP_LOAD_ON_CNTR_ZERO);

EPWM_setCounterCompareValue(myEPWM2_BASE, EPWM_COUNTER_COMPARE_B, 492);

EPWM_setCounterCompareShadowLoadMode(myEPWM2_BASE, EPWM_COUNTER_COMPARE_B, EPWM_COMP_LOAD_ON_CNTR_ZERO);

EPWM_disableActionQualifierShadowLoadMode(myEPWM2_BASE, EPWM_ACTION_QUALIFIER_A);

EPWM_setActionQualifierShadowLoadMode(myEPWM2_BASE, EPWM_ACTION_QUALIFIER_A, EPWM_AQ_LOAD_ON_CNTR_ZERO);

EPWM_setActionQualifierAction(myEPWM2_BASE, EPWM_AQ_OUTPUT_A, EPWM_AQ_OUTPUT_NO_CHANGE, EPWM_AQ_OUTPUT_ON_TIMEBASE_ZERO);

EPWM_setActionQualifierAction(myEPWM2_BASE, EPWM_AQ_OUTPUT_A, EPWM_AQ_OUTPUT_NO_CHANGE, EPWM_AQ_OUTPUT_ON_TIMEBASE_PERIOD);

EPWM_setActionQualifierAction(myEPWM2_BASE, EPWM_AQ_OUTPUT_A, EPWM_AQ_OUTPUT_HIGH, EPWM_AQ_OUTPUT_ON_TIMEBASE_UP_CMPA);

EPWM_setActionQualifierAction(myEPWM2_BASE, EPWM_AQ_OUTPUT_A, EPWM_AQ_OUTPUT_NO_CHANGE, EPWM_AQ_OUTPUT_ON_TIMEBASE_DOWN_CMPA);

EPWM_setActionQualifierAction(myEPWM2_BASE, EPWM_AQ_OUTPUT_A, EPWM_AQ_OUTPUT_LOW, EPWM_AQ_OUTPUT_ON_TIMEBASE_UP_CMPB);

EPWM_setActionQualifierAction(myEPWM2_BASE, EPWM_AQ_OUTPUT_A, EPWM_AQ_OUTPUT_NO_CHANGE, EPWM_AQ_OUTPUT_ON_TIMEBASE_DOWN_CMPB);

EPWM_disableActionQualifierShadowLoadMode(myEPWM2_BASE, EPWM_ACTION_QUALIFIER_B);

EPWM_setActionQualifierShadowLoadMode(myEPWM2_BASE, EPWM_ACTION_QUALIFIER_B, EPWM_AQ_LOAD_ON_CNTR_ZERO);

EPWM_setActionQualifierAction(myEPWM2_BASE, EPWM_AQ_OUTPUT_B, EPWM_AQ_OUTPUT_NO_CHANGE, EPWM_AQ_OUTPUT_ON_TIMEBASE_ZERO);

EPWM_setActionQualifierAction(myEPWM2_BASE, EPWM_AQ_OUTPUT_B, EPWM_AQ_OUTPUT_NO_CHANGE, EPWM_AQ_OUTPUT_ON_TIMEBASE_PERIOD);

EPWM_setActionQualifierAction(myEPWM2_BASE, EPWM_AQ_OUTPUT_B, EPWM_AQ_OUTPUT_NO_CHANGE, EPWM_AQ_OUTPUT_ON_TIMEBASE_UP_CMPA);

EPWM_setActionQualifierAction(myEPWM2_BASE, EPWM_AQ_OUTPUT_B, EPWM_AQ_OUTPUT_NO_CHANGE, EPWM_AQ_OUTPUT_ON_TIMEBASE_DOWN_CMPA);

EPWM_setActionQualifierAction(myEPWM2_BASE, EPWM_AQ_OUTPUT_B, EPWM_AQ_OUTPUT_NO_CHANGE, EPWM_AQ_OUTPUT_ON_TIMEBASE_UP_CMPB);

EPWM_setActionQualifierAction(myEPWM2_BASE, EPWM_AQ_OUTPUT_B, EPWM_AQ_OUTPUT_NO_CHANGE, EPWM_AQ_OUTPUT_ON_TIMEBASE_DOWN_CMPB);

EPWM_setDeadBandDelayPolarity(myEPWM2_BASE, EPWM_DB_FED, EPWM_DB_POLARITY_ACTIVE_LOW);

EPWM_setDeadBandDelayMode(myEPWM2_BASE, EPWM_DB_RED, true);

EPWM_setRisingEdgeDelayCountShadowLoadMode(myEPWM2_BASE, EPWM_RED_LOAD_ON_CNTR_ZERO);

EPWM_disableRisingEdgeDelayCountShadowLoadMode(myEPWM2_BASE);

EPWM_setRisingEdgeDelayCount(myEPWM2_BASE, 20);

EPWM_setDeadBandDelayMode(myEPWM2_BASE, EPWM_DB_FED, true);

EPWM_setFallingEdgeDelayCountShadowLoadMode(myEPWM2_BASE, EPWM_FED_LOAD_ON_CNTR_ZERO);

EPWM_disableFallingEdgeDelayCountShadowLoadMode(myEPWM2_BASE);

EPWM_setFallingEdgeDelayCount(myEPWM2_BASE, 20);

EPWM_enableGlobalLoadRegisters(myEPWM2_BASE, EPWM_GL_REGISTER_DBRED_DBREDHR);

EPWM_enableGlobalLoadRegisters(myEPWM2_BASE, EPWM_GL_REGISTER_DBFED_DBFEDHR);

}

//*****************************************************************************

//

// EPWMXBAR Configurations

//

//*****************************************************************************

void EPWMXBAR_init(){

myEPWMXBAR0_init();

}

void myEPWMXBAR0_init(){

XBAR_setEPWMMuxConfig(myEPWMXBAR0, XBAR_EPWM_MUX00_CMPSS1_CTRIPH);

XBAR_enableEPWMMux(myEPWMXBAR0, XBAR_MUX00);

}

//*****************************************************************************

//

// GPIO Configurations

//

//*****************************************************************************

void GPIO_init(){

myGPIO_Relay_init();

}

void myGPIO_Relay_init(){

GPIO_setPadConfig(myGPIO_Relay, GPIO_PIN_TYPE_STD);

GPIO_setQualificationMode(myGPIO_Relay, GPIO_QUAL_SYNC);

GPIO_setDirectionMode(myGPIO_Relay, GPIO_DIR_MODE_OUT);

GPIO_setControllerCore(myGPIO_Relay, GPIO_CORE_CPU1);

}

//*****************************************************************************

//

// INTERRUPT Configurations

//

//*****************************************************************************

void INTERRUPT_init(){

// Interrupt Settings for INT_myADCA_1

// ISR need to be defined for the registered interrupts

Interrupt_register(INT_myADCA_1, &INT_myADCA_1_ISR);

Interrupt_enable(INT_myADCA_1);

// Interrupt Settings for INT_myECAP0

// ISR need to be defined for the registered interrupts

Interrupt_register(INT_myECAP0, &ecap1ISR);

Interrupt_enable(INT_myECAP0);

// Interrupt Settings for INT_myECAP1

// ISR need to be defined for the registered interrupts

Interrupt_register(INT_myECAP1, &ecap2ISR);

Interrupt_enable(INT_myECAP1);

}

//*****************************************************************************

//

// SYNC Scheme Configurations

//

//*****************************************************************************

void SYNC_init(){

SysCtl_setSyncOutputConfig(SYSCTL_SYNC_OUT_SRC_EPWM1SYNCOUT);

//

// For EPWM1, the sync input is: SYSCTL_SYNC_IN_SRC_EXTSYNCIN1

//

SysCtl_setSyncInputConfig(SYSCTL_SYNC_IN_EPWM4, SYSCTL_SYNC_IN_SRC_EXTSYNCIN1);

SysCtl_setSyncInputConfig(SYSCTL_SYNC_IN_EPWM7, SYSCTL_SYNC_IN_SRC_EPWM1SYNCOUT);

SysCtl_setSyncInputConfig(SYSCTL_SYNC_IN_ECAP1, SYSCTL_SYNC_IN_SRC_EPWM1SYNCOUT);

SysCtl_setSyncInputConfig(SYSCTL_SYNC_IN_ECAP4, SYSCTL_SYNC_IN_SRC_EPWM1SYNCOUT);

SysCtl_setSyncInputConfig(SYSCTL_SYNC_IN_ECAP6, SYSCTL_SYNC_IN_SRC_EPWM1SYNCOUT);

//

// SOCA

//

SysCtl_enableExtADCSOCSource(0);

//

// SOCB

//

SysCtl_enableExtADCSOCSource(0);

}