24V步进电机线跟step、dir共线了一段距离,约1000mm。噪声如上图:

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

24V步进电机线跟step、dir共线了一段距离,约1000mm。噪声如上图:

您好

请问下如上的连接,-0.44V 的电压,对 DRV8434SPWPR 有多大影响?

能确定的是一定有影响,但是具体影响有多大,需要结合实际情况,对于您这种情况下的串扰是需要进行处理的,但是单论波形抛开实际情况不谈,不能直接评估影响有多大。

假如把 DRV8434SPWPR 前面串接的 100R 电阻,改成 1K 电阻,风险是不是会更小?

会有改善,但是这不是一个单纯的电阻增大,风险变小的问题。因为没有原理图,所以不能判断是不是风险更小了。

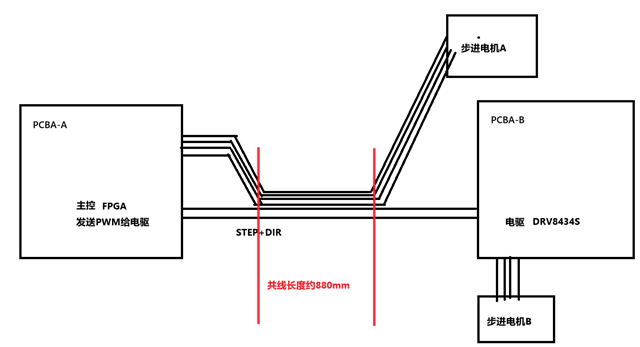

是一个系统的工程,涉及到多块PCB,信号的传输路径看这里:

STEP和DIR传输路径:【FPGA -> SN74LVC541APWR -> 100R电阻】 -》 480mm长连接线 -> 【转接板 -> 100R电阻】 -》 连接线长约1000mm -> 【100R电阻 -》DRV8434SPWPR】

其中连接线长约1000mm,这部分会有电机线共线走线约880mm.

能确定的是一定有影响,但是具体影响有多大,需要结合实际情况。

---

会导致电驱芯片异常烧坏吗?还是说影响电驱芯片正常工作?

1. CH2-A1-Y 是步进电机A的电机线信号波形。

2. 原理图和PCB涉及的板子数量偏多,不便于分享,请根据上述的示意图评估。

3. 这种噪声可能来自长线、环境噪声、EMI问题------噪声来自CH2-A1-Y的串扰,这个是确定的。

4. 为什么增加1K会导致逻辑错误?

5. 不加1K,增加一个 100R电阻+1nF电容做RC滤波是否可行?

6. 钳位二极管的方案我可以测试看看效果。有可能钳位二极管并不能将电压钳位到-0.3V以上。我们所用的钳位二极管型号:DS521-30LED02 (江苏长电/长晶)

您好

1. CH2-A1-Y 是步进电机A的电机线信号波形。

CH2-A1-Y 中存在阶跃,而 CH1-Step 中却没有任何阶跃脉冲,这对我来说不太清楚。请您解释一下这是否是由于您使用的特定操作条件造成的。

. 这种噪声可能来自长线、环境噪声、EMI问题------噪声来自CH2-A1-Y的串扰,这个是确定的。

为什么增加1K会导致逻辑错误?

在信号驱动器之间串联一个电阻,会形成一个低通 RC 滤波器,其中寄生电容由走线和输入引脚决定。因此,电阻越大,RC 时间常数就越大,从而增加达到逻辑高或低的时间。因此,建议串联电阻的阻值在 100 欧姆左右。

. 不加1K,增加一个 100R电阻+1nF电容做RC滤波是否可行?

您可以添加 RC 滤波器,但您应该考虑不要确保滤波后的上升时间足够快以满足 DRV8434s、输入逻辑时序

钳位二极管的方案我可以测试看看效果。有可能钳位二极管并不能将电压钳位到-0.3V以上。我们所用的钳位二极管型号:DS521-30LED02 (江苏长电/长晶)

我们来试试这个二极管,看看它对噪声的影响。在中频 10mA 时,最大 VF 为 0.35。用一个串联电阻来限制电流,并告诉我它对信号的影响。

另外,为了降低 EMI,您还可以执行以下操作:

1-屏蔽电线。

2- 扭绞电线。

3-隔离SGND和PGND。

CH2-A1-Y 中存在阶跃 ------

过冲吗 ?我的猜测可能是因为电机线太长了的缘故吧。这个最大值是28.8V,影响应该没有那么大。

在信号驱动器之间串联一个电阻,会形成一个低通 RC 滤波器,其中寄生电容由走线和输入引脚决定。因此,电阻越大,RC 时间常数就越大,从而增加达到逻辑高或低的时间。因此,建议串联电阻的阻值在 100 欧姆左右。------

100R 电阻已经有好几个了,总计约300R(3个100R电阻)

您可以添加 RC 滤波器,但您应该考虑不要确保滤波后的上升时间足够快以满足 DRV8434s、输入逻辑时序 ------

您发的截图我看不到。是信号的上升下降时间要在范围内吗?超过了会怎么样 ?

我们来试试这个二极管,看看它对噪声的影响。在中频 10mA 时,最大 VF 为 0.35。用一个串联电阻来限制电流,并告诉我它对信号的影响。 ------

串联电阻是放在钳位二极管前级是吧?钳位二极管前级有200R电阻,不过这个方案我还没有时间测试,预计6月6日会测试起来。

另外,为了降低 EMI,您还可以执行以下操作:1-屏蔽电线。 2- 扭绞电线。 3-隔离SGND和PGND。 ------

目前我们已经将EMI处理好了,在电机线上增加了 LC 处理的 。连接线不能做到更粗,改屏蔽电线会增加线径,结构空间不允许。

您好

STEP输入有一个数字边缘检测器,使其对噪声敏感,这可能会导致意外的阶跃脉冲(例如,对单个脉冲进行重复计数)。你有没有观察到任何意外的运动?这个可以详细说一下嘛?

STEP 输入中的边沿检测器旨在检测数字信号的边沿。 上升沿、当它从低电平变为高电平时、下降沿、当它从高电平变为低电平时。 电气噪声或信号反射可能会产生错误转换或微小的意外电压尖峰。 这些尖峰对于驱动器而言可能看起来是有效的数字边沿。 当发送一个 STEP 脉冲时、驱动器可能会看到两个上升沿(STEP 脉冲)而不是一个、并且电机移动两个步长而不是一个。 (双计数)。 我已询问您的应用程序中是否发生了此问题。 您需要检查电机运动是否有特定数量的步进脉冲、查看其是否正确。

靠近控制引脚(STEP和DIR)有一个 100R 电阻。

是否可以将靠近(STEP和DIR)引脚的100R电阻换成磁珠?不过这个需要测试来看效果。

两者都可降低 EMI 噪声。 串行器电阻器用作低通滤波器、串行器磁珠可阻止高频 EMI。 您可以使用磁珠替代电阻器;使用铁氧体磁珠时、负电压可能会降低到规格范围内

您好

看规格书中,是对脉冲宽度有要求的,我们的噪声宽度小于100ns.

而且噪声脉冲低电平最大值,没有达到1.5V(获取高电平的最小值)

因此,这在您的申请中不会成为问题。

请将添加系列磁珠的结果更新给我。