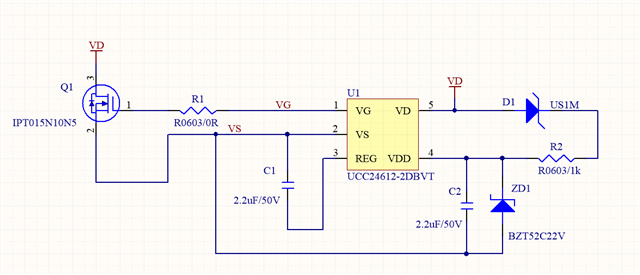

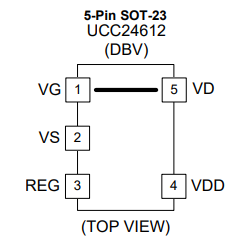

器件型号:UCC24612-2DBVT

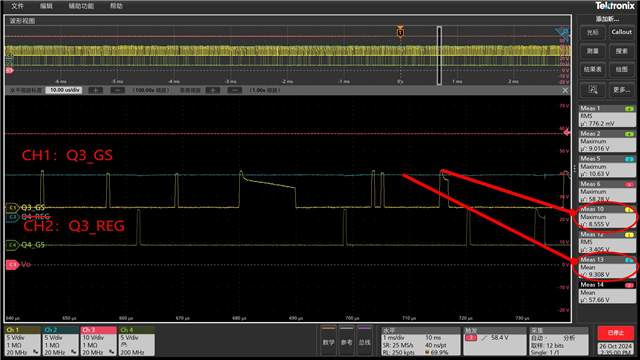

问题描述:使用UCC24612-2DBVT做全桥同步整流,当系统输出空载时,驱动产生延迟关断,表现为驱动波形占空比不固定,来回大范围抖动,导致mos整流桥轻微直通。

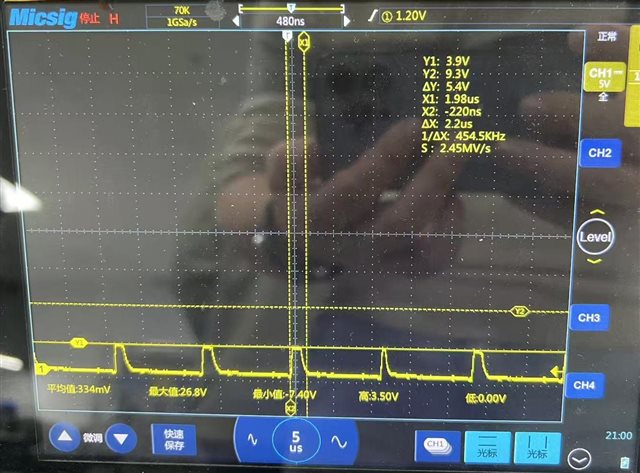

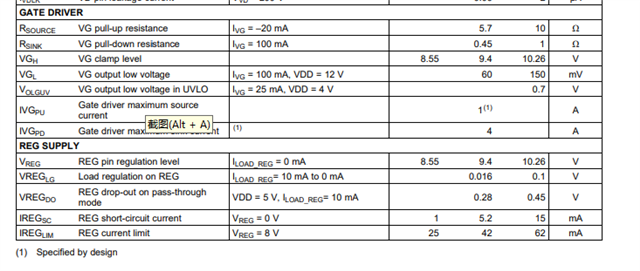

进一步测试发现,当所用mos输入电容Ciss为6nF时,驱动高电平为正常的9.2V,驱动波形正常;当所用mos 输入电容Ciss为16nF,测试芯片VREG为正常的9.2V,但是驱动gs高电平仅为为VGH=7.2V(低于规格书VGH min:8.55V),部分芯片产生上述驱动占空比抖动,并导致直通。

改进测试后发现,增加驱动电阻,也会导致驱动高电平低于规格书VGH min=8.55V,继续增大驱动电阻,VGH降低到4.2V左右。

所以,有如下问题请教:

1、如果要保证 UCC24612-2DBVT VGH不低于规格书中最小值8.55V,支持mos Ciss的最大值是多少?

2、UCC24612-2DBVT RSOURCE值为5.7~10Ω,mos 内部G极电阻1.4Ω,保证IVGPU不超过1A,不同Ciss下推荐的驱动电阻Rg是多少(根据上述测试结果,Ciss、Rg越大,VGH越小)

3、当驱动高电平VGH=7.2V时,只有部分芯片产生异常(占空比宽范围抖动),即部分芯片出线不良,占比约25%,出现此不良的原因是什么?a)芯片设计缺陷:VGH低于VGH min:8.55V,有一定概率出现不良?2)芯片来源不可靠,部分芯片存在质量问题

期待您的专业答复,谢谢!