C6678的core1~7核加载成功;但core0加载失败,不清楚什么原因;请尽快协助分析和解决:

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好,

已为您催过工程师,您可以访问(+) TMS320C6678: TMS320C6678's core0 fails to load - Processors forum - Processors - TI E2E support forums英文原帖了解最新进展

如果您用的是TI-C6678 EVM,这个问题会很好解决,请您不必担心。

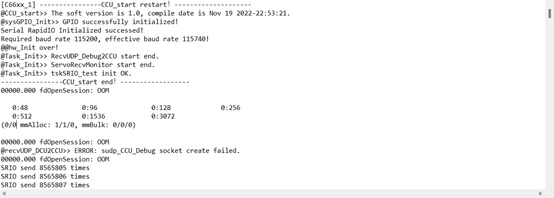

首先进行检查,无论结果否成功,请用XDS和CCS做test connection和target connection。

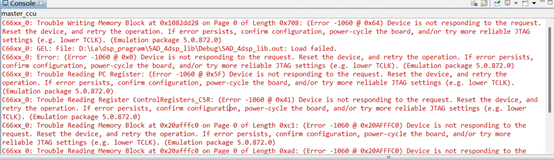

请按照本常见问题解答中给出的步骤发布您的 GEL 输出控制台消息。

如果您成功完成了以上两步,请尝试加载像平台测试程序这样的工作示例并运行;观察行为和输出。

Katherine Wang 您好!

感谢您的回复,现在出问题的不是TI TI-C6678 EVM,是我们自己设计一个板卡;

出现这样的问题,需要排查哪些哪些设计点?

原理图设计上主要排查哪些点?

PCB设计上主要排查哪些点?

软件代码上需要排查哪些点?

请您参阅以下步骤,尝试在eby上解决。

1. 比较“C6678 EVM”与“your-Custom-EVM”的原理图。

2. 您可以在此处找到 C6678 EVM 的原理图:https://www2.advantech.com/Support/TI-EVM/6678le_sd.aspx

3. 在定制板、原理图中,特别关注 XDS 板载仿真器部分。

4. 如果 XDS-Emulator 部分没有差异,请继续执行以下自定义板与 XDS 和 CCS 的“测试连接”步骤。

---

步骤1:

检查是否有针对仿真器/调试模式的 DIP 开关设置。

例如,在 TI-C6678 EVM 中,它被称为“NO -boot 模式”。

DIP 开关设置 - “NO-Boot-Mode” - 适用于 Ti-C6678 EVM

SW6:1 1 1 1

SW5:1 1 1 1

SW4:1 1 1 1

SW3:0 1 1 1

首先请按照此处给出的步骤执行“测试连接过程”,然后将输出控制台消息发布给我。

---

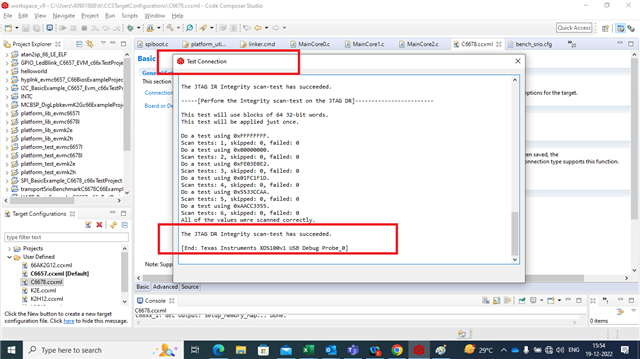

C6678 EVM 和 TEST -CONNECTION 选项的 cxml 文件设置:

================================================ =========

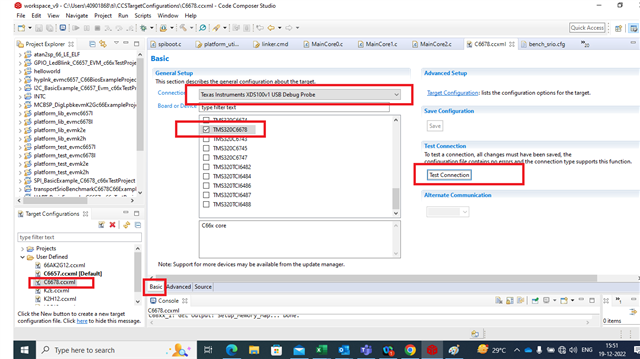

CCS中的测试连接输出:

===========================

----

完成 - 成功的 JTAG 连接输出将如下所示:

================================================ =============

---

The JTAG IR instruction path-length is 6 bits. The test for the JTAG DR bypass path-length succeeded. The JTAG DR bypass path-length is 1 bits. -----[Perform the Integrity scan-test on the JTAG IR]------------------------ This test will use blocks of 64 32-bit words. This test will be applied just once. Do a test using 0xFFFFFFFF. Scan tests: 1, skipped: 0, failed: 0 Do a test using 0x00000000. Scan tests: 2, skipped: 0, failed: 0 Do a test using 0xFE03E0E2. Scan tests: 3, skipped: 0, failed: 0 Do a test using 0x01FC1F1D. Scan tests: 4, skipped: 0, failed: 0 Do a test using 0x5533CCAA. Scan tests: 5, skipped: 0, failed: 0 Do a test using 0xAACC3355. Scan tests: 6, skipped: 0, failed: 0 All of the values were scanned correctly. The JTAG IR Integrity scan-test has succeeded. -----[Perform the Integrity scan-test on the JTAG DR]------------------------ This test will use blocks of 64 32-bit words. This test will be applied just once. Do a test using 0xFFFFFFFF. Scan tests: 1, skipped: 0, failed: 0 Do a test using 0x00000000. Scan tests: 2, skipped: 0, failed: 0 Do a test using 0xFE03E0E2. Scan tests: 3, skipped: 0, failed: 0 Do a test using 0x01FC1F1D. Scan tests: 4, skipped: 0, failed: 0 Do a test using 0x5533CCAA. Scan tests: 5, skipped: 0, failed: 0 Do a test using 0xAACC3355. Scan tests: 6, skipped: 0, failed: 0 All of the values were scanned correctly. The JTAG DR Integrity scan-test has succeeded. [End: Texas Instruments XDS100v1 USB Debug Probe_0]