作者RJ Hopper

** 这是Analog Wire RF取样博客系列的第10篇。 **

我在之前的博文中论述了无线电频率(RF)取样结构对宽带系统的优势,但有些系统的运行需要中等带宽,或有其它重点考虑的因素。有源天线阵使用多个专用于产生比单个元件更集中的辐射模式天线。这种集中的模式可将天线增益增加到预定目标或用户,并可同时对波束图型以外区域提供干扰抑制,从而无需过多信号带宽。

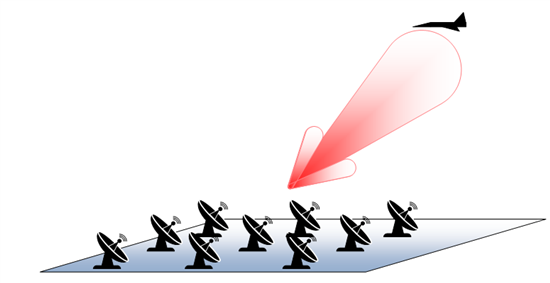

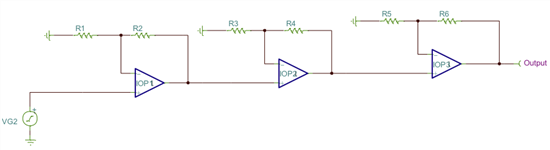

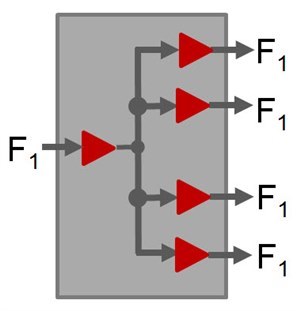

雷达阵列就是一种用于精确定位空间目标的有源天线系统。图1中所示的简单的3×3阵列系统能够导引两个维度的波束来追踪目标。

图 1:3×3雷达天线阵列

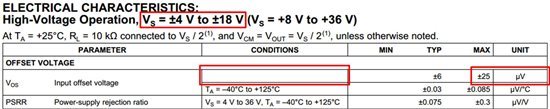

每个天线元件都需要有自己的接收机。较小的阵列可能使用八个元件;非常大的阵则会使用数以千计的元件。这些系统需要大量的接收机,因此每个接收机必须低成本且高功率;并且这些系统需要高动态范围的性能,从而在背景噪声和干扰中辨别目标。

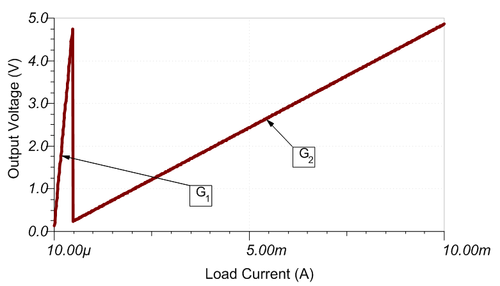

TI设计的700-2700MHz双通道接收机和16位ADC及100MHz…

模拟

模拟 汽车

汽车 DLP® 技术

DLP® 技术 嵌入式处理

嵌入式处理 工业

工业 电源管理

电源管理