我在使用 CDCM6208 进行时钟分配设计时,遇到了一个异常问题:芯片的 PLL 在运行过程中会周期性地锁定后又失锁,PLL_UNLOCK 引脚状态在高低之间不断切换,表现为反复进入“锁定 → 失锁 → 再锁定”的循环。

以下是我的配置与使用情况:

我在使用 CDCM6208 进行时钟分配设计时,遇到了一个异常问题:芯片的 PLL 在运行过程中会周期性地锁定后又失锁,PLL_UNLOCK 引脚状态在高低之间不断切换,表现为反复进入“锁定 → 失锁 → 再锁定”的循环。

以下是我的配置与使用情况:

Hi All,

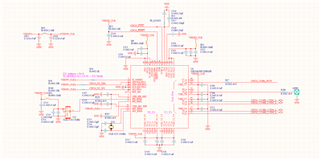

我使用CDCM6208V2G作为主时钟芯片发生器,但是始终无法正确配置,以至于CDCM6208一直不工作,原理图如下:

将Y4Y5设置成125M LVDS给FPGA,Y6Y7设置成LVCOMS单端25M给以太网芯片使用。原理图配置使用的I2C接口,SI_MODE[1:0] = 2‘b 01,RESET使用外部MCU控制,RESET = 0;delay…

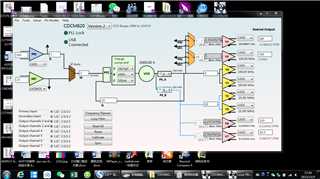

我选的是V1版本的pin mode下的0x03号配置,属于synthesizer mode还是jitter cleaner mode?

属于哪一个mode不是软件专门设置的,还是选的loop filter的内部和外部电容电阻参数共同决定的?

如果某一路输出时钟没有用到,能否在pin mode模式下选择一种8路都输出的配置?

没有用到的这一路,输出buffer的电源VDD_Yx/VDD_Yx_Yy怎么处理?

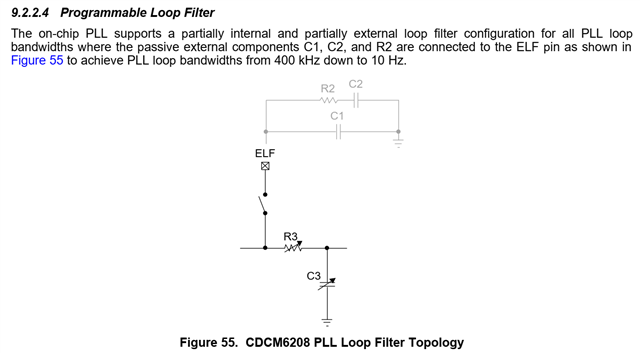

ELF管脚作为Loop filter使用,两组电路,第一组内部R3和C3, 第二组外部的R2, C2和C1。这两组是同时工作的,还是应互相替代由软件选择使用第一组还是第二组?

在Pin mode 模式下,R3和C3是不是根据PIN MODE就已经是确定的,而不需要HOST通过通讯接口进行设置?

根据产品手册,如果SYNCN存在从0到1的跳变,那么这个跳变触发时钟输出,所有输出时钟的上升沿对齐。

如果SYNCN管脚能否悬空(内部上拉)或者接高电平,管脚状态为1,CDCM6208的输出时钟是否是对齐的?

我的电路用的芯片是cdcm6208v1,芯片的所有供电都是3.3v,输入时钟采用第一路输入,用3.3V的25MHz单端晶振,负端用1K下拉到地,第二路时钟输入的正负都是分别用1K电阻下拉到地,采用SPI方式进行寄存器配置,所有时钟输出电压都是3.3v供电,且都采用LVDS,目前发现Y0和Y1配置成212.5M,发现实际输出只有127MHz左右

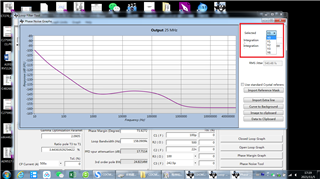

大家好啊:请教一下,使用EVM software v3.24 进行 phase noise Tool 仿真异常,cdcm6208 一共8个通道,为什么这个选项里面只有01236这几个通道,我要用的通道都没有 ;我的配置

大家好啊:请教一下,使用EVM software v3.24 进行 phase noise Tool 仿真异常,cdcm6208 一共8个通道,为什么这个选项里面只有01236这几个通道,我要用的通道都没有 ;我的配置 , 等着写报告,需要仿真结果,急啊

, 等着写报告,需要仿真结果,急啊

Hi Ti工程师 目前在使用cdcm6208 芯片Y0_P/Y0_N, Y1_P/Y1_N, Y2_P/Y2_N, Y3_P/Y3_N,管脚没有差分时钟输出,时钟不能正常输出导致dsp不能工作。 下面是原理图和代码,请帮忙看下:

已进行的测试:

1.STATUS0管脚为低电平;

2.SI_MODE0,SI_MODE1为低电平(spi配置);

3.SEC_REFP为25Mhz的时钟输入;

4.SYNC/PDN/RESETN 为高电平1.8V;

5.SPI相应的管脚在示波器上抓取波形…