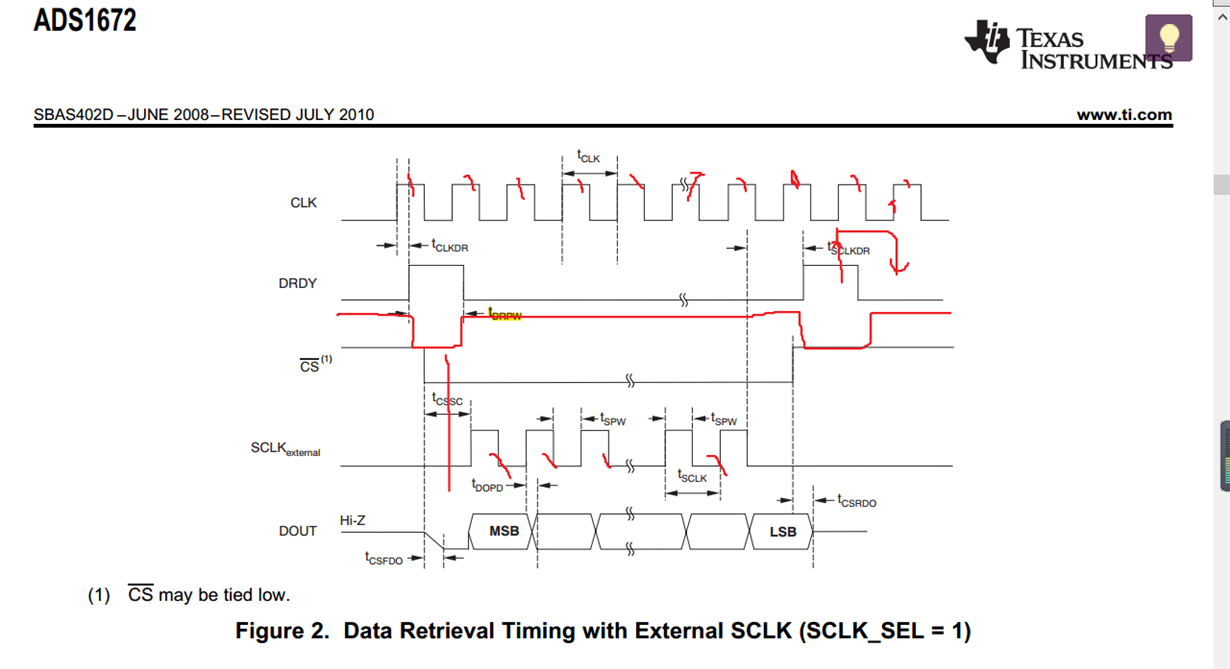

最近在使用TI的ADS1672。用CPLD(MAXII)驱动。ADC的工作时钟是20M,采用外部读时钟也是20M。

现在的问题是读的数据有时候会出错。每次读1024个数据就会有三四个不正常数据(此数据很大或者很小)。

我把驱动文件贴出来放附件里。还有就是Read引脚我用的是低脉冲触发的那个引脚。望大神教我。

第一次在TI论坛发帖,教教我

module ads1672_drive( sys_clk20m, //CPLD系统时钟

sys_rst, //CPLD复位信号

ready_port, //数据采集完成端口

data_port, //数据采集端口

device_cs, //器件片选

work_clk20m, //ADS1672工作时钟

read_clk20m, //数据读时钟

Buffer_24bit //实时采集的数据

);

input sys_clk20m;

input sys_rst;

input ready_port;

input data_port;

output reg device_cs;

output work_clk20m;

output read_clk20m;

output reg [23:0] Buffer_24bit;

reg Pulse_NowSta; //ready的脉冲最新状态

reg Pulse_OldSta; //ready的脉冲前一状态

wire Rising_Edge; //上升沿

wire Falling_Edge; //下降沿

assign work_clk20m = sys_clk20m;

always@( posedge sys_clk20m or negedge sys_rst)

if( !sys_rst) begin

Pulse_NowSta<=1'b1; //这两个状态的初始值和信号源的初始状态总是一致的,才是最安全的

Pulse_OldSta<=1'b1;

end

else begin

Pulse_NowSta<=ready_port;

Pulse_OldSta<=Pulse_NowSta;

end

assign Rising_Edge =(~Pulse_OldSta)&Pulse_NowSta;

assign Falling_Edge=(~Pulse_NowSta)&Pulse_OldSta;

//读取24bit数据需要24个时钟,数据读完毕需要关闭读时钟

reg ReadClk20m_EN;

reg [4:0] ReadClk20m_Cnt;

reg Buff_Sta;

always@( posedge sys_clk20m or negedge sys_rst)

if( !sys_rst ) begin

device_cs <=1'b1;

ReadClk20m_EN<=1'b0;

end

else begin

if( ReadClk20m_Cnt==5'd24 ) begin

device_cs <=1'b1;

ReadClk20m_EN<=1'b0;

end

else if(Falling_Edge ) device_cs<=1'b0;

else;

if(Rising_Edge) ReadClk20m_EN<=1'b1;

end

/*

always@( posedge sys_clk20m or negedge sys_rst)

if( !sys_rst ) Buff_Sta<=1'b0;

else if(ReadClk20m_Cnt==5'd24) Buff_Sta<=1'b0;

else if(ReadClk20m_EN) Buff_Sta<=1'b1;

else Buff_Sta<=1'b0;

*/

assign read_clk20m=(ReadClk20m_EN==1'b1)?sys_clk20m:1'b0;

reg [23:0] Temp_Buff; //24bit数据读取临时缓存

//数据采集

always@( posedge sys_clk20m or negedge sys_rst)

if( !sys_rst ) begin

ReadClk20m_Cnt<=5'd0;

Temp_Buff <=24'd0;

Buffer_24bit <=24'd0;

end

else begin

if(ReadClk20m_EN) begin

ReadClk20m_Cnt<=ReadClk20m_Cnt+1'b1;

case(ReadClk20m_Cnt)

0: Temp_Buff[23]<=data_port;

1: Temp_Buff[22]<=data_port;

2: Temp_Buff[21]<=data_port;

3: Temp_Buff[20]<=data_port;

4: Temp_Buff[19]<=data_port;

5: Temp_Buff[18]<=data_port;

6: Temp_Buff[17]<=data_port;

7: Temp_Buff[16]<=data_port;

8: Temp_Buff[15]<=data_port;

9: Temp_Buff[14]<=data_port;

10: Temp_Buff[13]<=data_port;

11: Temp_Buff[12]<=data_port;

12: Temp_Buff[11]<=data_port;

13: Temp_Buff[10]<=data_port;

14: Temp_Buff[9] <=data_port;

15: Temp_Buff[8] <=data_port;

16: Temp_Buff[7] <=data_port;

17: Temp_Buff[6] <=data_port;

18: Temp_Buff[5] <=data_port;

19: Temp_Buff[4] <=data_port;

20: Temp_Buff[3] <=data_port;

21: Temp_Buff[2] <=data_port;

22: Temp_Buff[1] <=data_port;

23: Temp_Buff[0] <=data_port;

24: begin

Buffer_24bit<=Temp_Buff;

// Buffer_24bit<=24'd98765;

ReadClk20m_Cnt<=5'd0;

end

default: ;

endcase

end

end

endmodule