Part Number: TIOS102

Other Parts Discussed in Thread: TIOX1X2XEVM, , TIOS101

您好,我们在刚才的测试中发现,在测试芯片下管的输出漏电流时,如果在导通下官后又迅速关断,测出的漏电流值为3.7mA,如果导通和关断时间间隔较大时,测得漏电流为550μA。

请教一下这个3.7mA是什么原因?下管在快速通断时不能完全关断吗?

测试中EN恒为3.3V,使用IN控制输出。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Part Number: TIOS102

Other Parts Discussed in Thread: TIOX1X2XEVM, , TIOS101

您好,我们在刚才的测试中发现,在测试芯片下管的输出漏电流时,如果在导通下官后又迅速关断,测出的漏电流值为3.7mA,如果导通和关断时间间隔较大时,测得漏电流为550μA。

请教一下这个3.7mA是什么原因?下管在快速通断时不能完全关断吗?

测试中EN恒为3.3V,使用IN控制输出。

您好,

它们是在 TIOx1x2xEVM 上还是在其自己设计的电路板上运行测试? 请提供实际原理图或详细图、其中显示了测试设置中引脚 VCC、OUT、GND、IN 和 EN 的所有元件、元件值以及测量值的电压电平。 此图甚至未显示器件在 VCC 和 GND 之间连接了电源。

您是否还可以用某种形式的时间值和“快速“来定义“大开/关时间间隔“? 这些术语是否以 ms、s、min、hours 等为单位?

一旦我获得更多信息并了解测试设置中使用的引脚电压电平和元件值、就可以更好地确定器件在哪种状态下运行并查看测试结果。

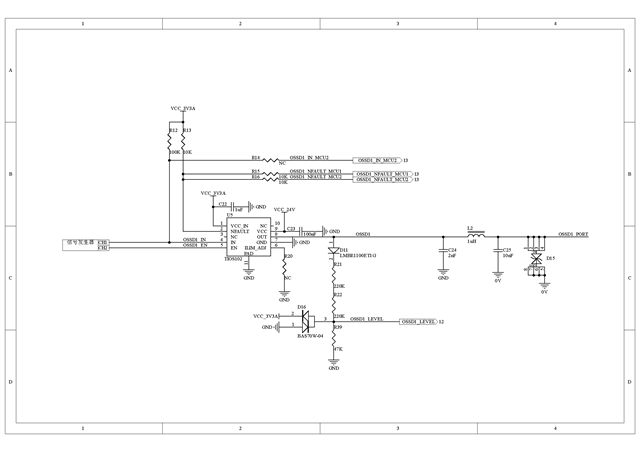

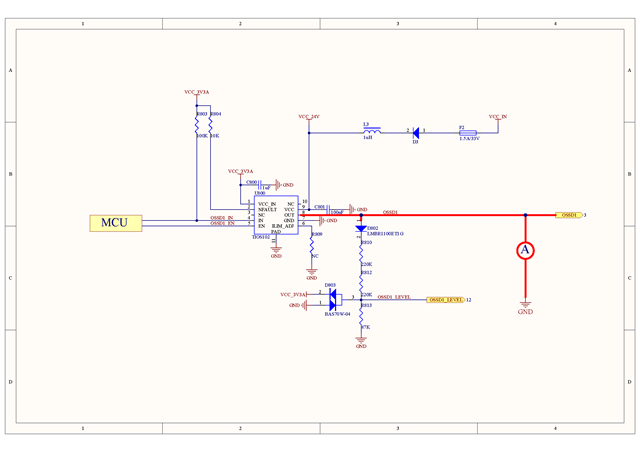

1.原理图

试验是在自己设计的电路板上执行的,后来重新做了测试,基本原理图见下图。

测试下管的漏电流时,OSSD1_PORT 经串联的负载电阻和电流表连接到24V电源;

测试上管的漏电流时,OSSD1_PORT 经串联的负载电阻和电流表连接到0V电源。

信号发生器CH1直接控制TIOS102的EN引脚;CH2直接控制TIOS102的IN引脚。

2.试验1

EN引脚恒输入3.3V电平,TIOS102被使能;

IN引脚输入周期10s的方波,以控制TIOS102的上管导通或下管导通。使用电流表记录负载线电流。

下管导通时,负载电流203mA,下管关断时,测得漏电流4.4mA。 漏电流与外部负载相关,如负载200Ω时,导通电流115mA,漏电流2.5mA。(视频1)

上管导通时,负载电流197mA,上管关断时,漏电流50μA。该漏电流与负载无关。(视频2)

下管工作电流测试:

上管工作电流测试:

3.试验2

将EN设置为低电平,测得下管漏电流为100μA-110μA,上管漏电流40μA。

以上示波器展示的波形中,CH1为电路输出OSSD1波形,CH2为IN波形。

4. 试验3

使用信号发生器控制输出的试验中,设置EN恒为高电平时,尚未稳定测得下管漏电流为550μA的情况。

如果在IN为低电平时(下管关断),将EN置低后再置高,可测得550μA漏电流。

您好,

感谢您提供更多信息。 我对他们的意见有很好的理解。

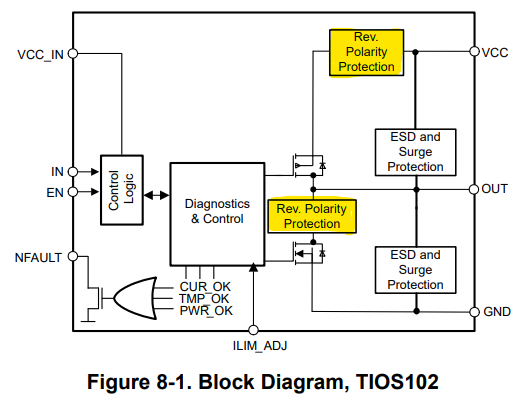

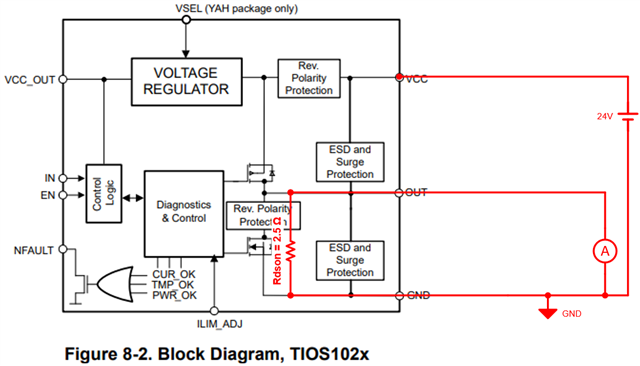

TIOS102 具有主动监控反极性保护方法、可防止接线错误的应用。 如果在相应的高侧或低侧驱动器被启用和激活时 OUT 引脚的电压电平大于 VCC 或小于 GND、则器件将禁用驱动器并阻止电流流经驱动器。

需要检测到 OUT 引脚与 VCC 或 GND 之间的电压差 >100mV,否则将触发反极性保护电路并禁用驱动器。

具体来说、如果启用了高侧驱动器、OUT 引脚上的电压将需要大于 VCC + 100mV。

同样、如果启用了低侧驱动器、则 OUT 引脚上需要低于 GND-100mV 的电压。

利用 TIOS102、IN 引脚控制在 EN 引脚为高电平时哪个驱动器处于活动状态。 然后 EN 引脚切换为高电平和低电平、从而使 OUT 引脚在驱动电压和 Hi-Z 状态之间转换。 但通常、对于高侧或低侧驱动器、外部负载是固定的。

此应用在推挽配置中同时使用高侧和低侧驱动器、但外部负载不变以匹配。 这会导致在外部负载和驱动器上的内部 Rdson 之间形成环路。

驱动器晶体管上的 Rdson 通常为 2.5 欧姆。 这意味着当高侧驱动器处于活动状态时、VCC 和 OUT 引脚之间存在 2.5 Ω 的阻抗、而当低侧驱动器处于活动状态时、OUT 和 GND 之间存在 2.5 Ω 的阻抗。

OUT 和 VCC 或 GND 引脚之间的外部负载电阻与驱动器中的 Rdson 电阻并联。

由于反极性保护电路需要引脚之间存在 100mV 的电压差、因此驱动器将在“电阻模式“下运行、并且 RDSon 上必须有足够的电流流过、以便在引脚之间产生 100mV 的电压差、从而使驱动器在禁用状态下进入“二极管阻断模式“、并阻止电流流动。

这解释了他们说漏电流随外部负载变化的原因、以及如果负载电流增加(即 300mA)、为什么会减少到 560uA。

此外、如果 EN =低电平、则驱动器被禁用、泄漏电流很小、因为驱动器上没有 2.5 欧姆的电阻路径、并且驱动器在二极管阻断模式下运行。

较旧的 TIOS101 器件在驱动器栈中使用物理阻断二极管来阻止任何电流反向流动、并将其性能与我了解客户预期的情况保持一致。 不过、这些二极管会导致驱动器上产生较大的压降、从而增加功率耗散和器件温度。

当 TIOS102 连接错误或检测到较大故障条件时、使用这种较新的检测方法来保护器件免受损坏。 但根据 Rdson 的确切值、器件会在驱动器上消耗 20 –30mA、直到检测到 100mV 差异。

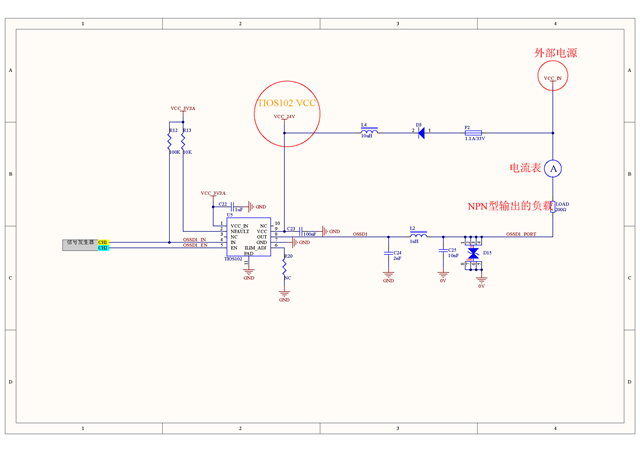

您好,我们目前应用方案是使用TIOS的推挽模式,同时兼容PNP输出和NPN输出。

看了您的回复,我突然意识到一个问题。NPN型输出上电源于TIOS102的电源之间有压差,见图。VCC_24V同时为其他电路供电,二极管压差有0.5V。

下管漏电流较大是不是因为以下原因?不知道分析是不是正确?

外部电源与TIOS102的VCC引脚之间存在0.5V压差。下管关闭上管导通时,上管MOSFET导通有2.5Ω导通电阻,与外部负载串联,此时测得的漏电流路径为:

外部电源→电流表→负载电阻→TIOS102上管导通电阻→TIOS102的VCC。

也就是说,测得的漏电流流过的是上管,而不是下管。

如果负载阻值较大,流过上管的反向电流较小,产生压降低于100吗V,不符合反极性保护的条件,所以持续产生mA级的漏电流。

如果负载阻值较小,流过上管的反向电流较大,产生压降超过100mV时,上管关断(二极管阻断),通过上管的漏电流被阻断,只有通过下管的550μA漏电流。

---

我们把24V电源线上二极管D3短接,测得的漏电流就在合理范围内了。

---

我们使用TIOS102芯片推挽输出的方式兼容PNP型和NPN型。

对NPN型,要关断下管打开上管时,先将EN拉低,再将IN拉低,再将EN拉高,此时输出高电平。

这种控制逻辑会有问题吗?

您好,

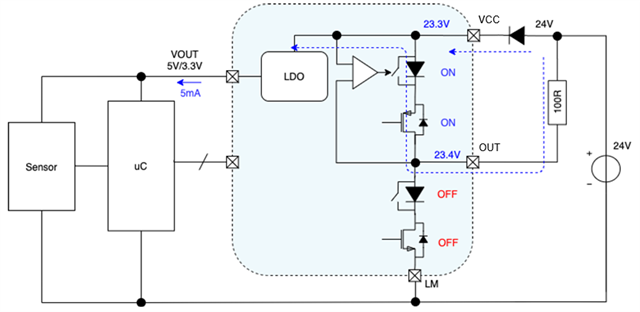

是的、我们之前遇到过类似的问题、客户在 24V 电源和 VCC 引脚之间放置了一个二极管、然后在 24V 主电源之间放置了一个上拉电阻器。 由于二极管压降、这确实会导致 OUT 和 VCC 引脚之间出现电压差。 当高侧驱动器被启用时、OUT 引脚连接到 VCC 引脚、该引脚的电压低于连接到外部上拉电阻器的电压。 这会导致外部电阻器上出现压降、而 TIOS102 将需要足够的电流流过晶体管的 2.5 Ω Rdson、以在 OUT 和 VCC 引脚之间产生 100mV 的差值、进而触发反极性检测比较器、使高侧驱动器被禁用并进入二极管阻断模式。

漏电流流入器件、作为 VCC 的第二个源

下图展示了器件的 LDO 版本的情况。 客户正在使用非 LDO 版本、但该器件仍将内部 LDO 用于数字内核、外部无法访问、因此漏电原理是相同的。 TIOS102 通过流入 VCC 和 OUT 引脚的电流组合进行供电。

如果负载阻值较大,流过上管的反向电流较小,产生压降低于100吗V,不符合反极性保护的条件,所以持续产生mA级的漏电流。

反极性保护电路旨在保护器件免受误接线的影响、误接线可能导致高电流、从而损坏器件。 在过去的器件(包括 TIOS101)中、驱动器栈中使用了实际二极管来阻止任何反向电流。 但在正常运行期间、这些二极管还会导致驱动器上出现较大的压降、从而导致更高的功率耗散。 因此、这些固定二极管已替换为检测电路、该电路可在接线错误问题时保护器件、从而实现更小的驱动器压降和更小的功率耗散。

其他竞争器件使用相同的方法、遗憾的是、对于客户的应用、这是引脚之间的电压比较器、它无法检测到不会损坏收发器本身的少量反向电流。

我们把24V电源线上二极管D3短接,测得的漏电流就在合理范围内了。

是的、这是预期结果、因为这会导致外部 200 欧姆上拉电阻器两侧之间产生非常小的电压差。当驱动器导通时,二极管和晶体管的导通电阻(Rdson)与200欧姆上拉电阻并联形成串联通路,至少会产生0.5V的电压差,从而使电流流过200欧姆电阻。

二极管上的短路会导致 200 欧姆上拉电阻器两侧之间产生非常小的电压差、并产生可忽略不计的电流。

我们使用TIOS102芯片推挽输出的方式兼容PNP型和NPN型。

对NPN型,要关断下管打开上管时,先将EN拉低,再将IN拉低,再将EN拉高,此时输出高电平。

这种控制逻辑会有问题吗?

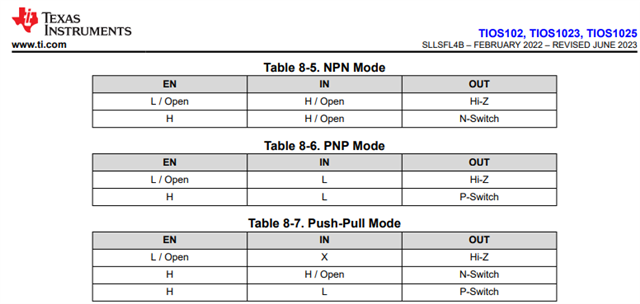

您可以在数据表中找到不同模式的逻辑表。 EN = L时,OUT 引脚出现高阻态(HI-Z)。当 EN = H 时、OUT 引脚将跟随 IN 引脚电压。 对于推挽操作、您可以保持 EN = H、只需更改 IN 引脚即可在两个驱动器之间切换。 但是、如果您希望在状态变化之间使 OUT 为 Hi-Z、可以首先使 EN = L、然后改变 IN 引脚的状态,最后再将 EN 设置为 H。

您好,

我们后来又简单做了一个测试,测试原理图见下图。

TIOS102的OUT不接其他负载,直接通过电流表接GND。

当把TIOS的下管打开,上管关闭时,仍可以测到3.38mA的漏电流。

当改变外部供电VCC_IN的电压时,该漏电流也会变化。大概趋势是电压降低,漏电流增大。电压升高,漏电流减小。供电19V的时候测得漏电流约3.6mA,供电29V是测得漏电流约3.2mA。

但如果在OUT与电流表之间与电流表串联一个负载,测的的漏电流为210μA左右。

所以请教下,这种OUT直接接地(电流表相当于短路)。将上管关闭测得的漏电流是怎样产生的呢?

感谢。

您好,

我很抱歉耽误我的回复、因为我在本周的大部分时间都无法使用 E2E。

当把TIOS的下管打开,上管关闭时,仍可以测到3.38mA的漏电流。

当下部管打开时、OUT 和 GND 引脚将通过驱动器晶体管在内部连接、Rdson 电阻约为 2.5 欧姆。 您基本上创建了一个环路、其中电流表和 Rdson(2.5 欧姆)在 OUT 和 GND 引脚之间并联。 在某些外部条件下、电流可能会流过 OUT 引脚、而不是 GND 引脚流向外部电源 GND、这正是我认为发生的情况。 一些~μ A 3mA 电流正在通过 OUT 引脚找到连接到外部电源 GND 的路径、而不是完全流经器件 GND 引脚。

在 OUT 引脚和电流表之间放置一个串联电阻将增加 OUT 引脚和外部电源 GND 之间的该电阻、并导致器件的电源电流从器件 GND 引脚流出、该引脚具有连接到外部电源 GND 的电阻路径要低得多。 这就是为什么在 OUT 引脚上使用串联电阻时只会看到大约 210uA 的电流。