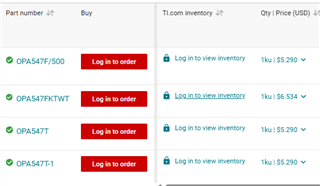

Other Parts Discussed in Thread: OPA593EVM, ALM2403-Q1, OPA547, OPA593, OPA547EVM

主题中讨论的其他器件: OPA547、 OPA593、 OPA547EVM、OPA593EVM

工具/软件:

我购买了 ALM2403-Q1 双电源运算放大器。

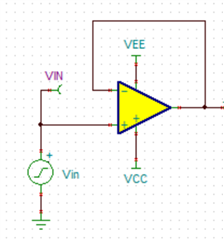

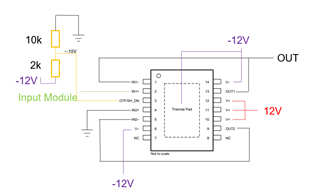

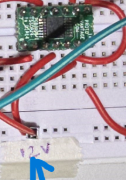

已建立的连接:

引脚1:NI FPGA GND

Pin2:NI FPGA 模拟输出 CH1

引脚10: +12V

引脚14:-12V

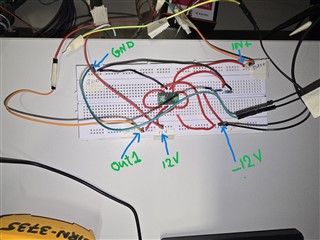

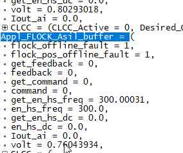

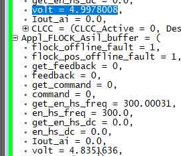

引脚13 ( 电流放大器 CH1的输出通道)处的电压始终为0V。

请帮助确定问题。

我已将 IC 安装在14引脚 IC 适配器上。