Other Parts Discussed in Thread: SN65HVD73, SN65HVD76, SN65HVD70, TMS320F280049, C2000WARE

主题中讨论的其他器件:SN65HVD73、 SN65HVD76、 SN65HVD70、 C2000WARE

你(们)好

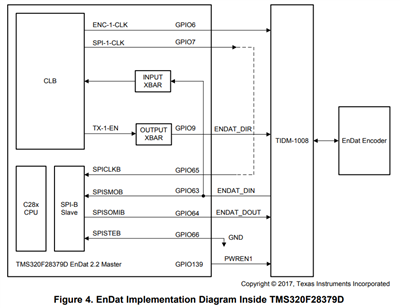

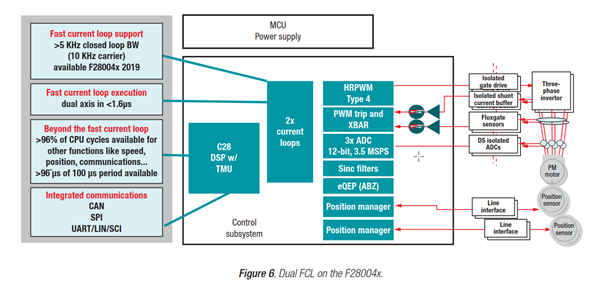

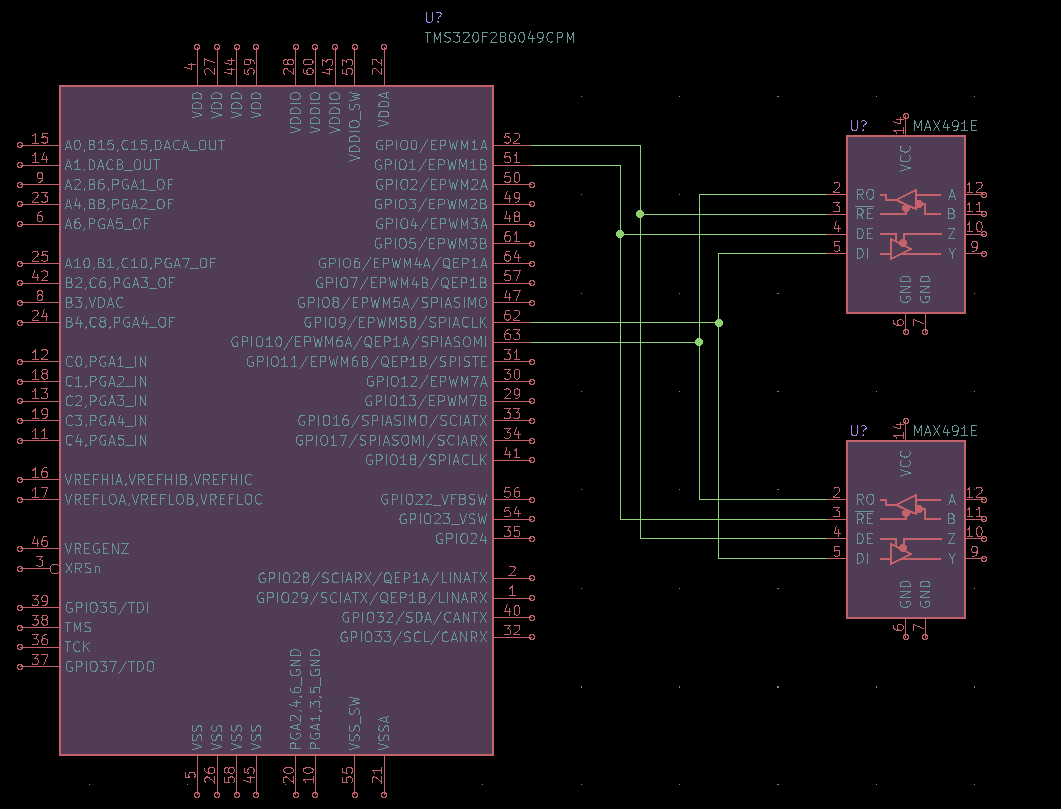

我正在考虑使用 TMS320F28004x 系列来开发具有2个绝对编码器的双轴驱动系统。 据我所知、使用绝对编码器功能需要 SPI 外设(与 CLB 一起)。 是否仍然可以将2个绝对编码器与1个 SPI 同时使用以进行正常通信?

感谢你的帮助