主题中讨论的其他器件:LAUNCHXL-F28379D

在过去的几周里、我一直与 TI Guru Ki RE 保持一致:当 DSS 脚本使用 asm (" :)构造以标记 DSS 脚本定义断点的代码中的位置。 起初、我认为问题出在 TI 演示板的错误构建上。 我最近的测试使用了5个不同的 TI 演示板、一个 controlCARD 和4个不同的 LaunchXL-F28379D 板。 都表现得相同。 下面是我的测试说明。

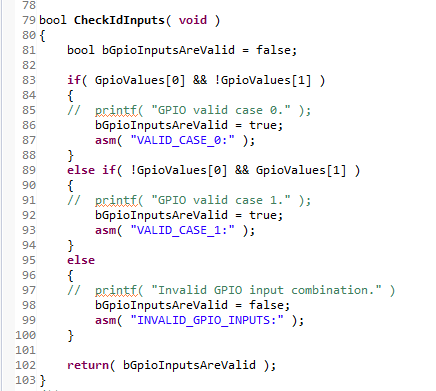

该测试程序从两个 GPIO 引脚(52和67)读取数据。 如果一个输入为高电平、另一个为低电平、则测试软件成功。 如果 GPIO67为低电平且 GPIO52为高电平、则发生 VALLED_CACT_0。 如果 GPIO67为高电平且 BPIO52为低电平、则发生 VALICAL_case_1。 如果两个引脚匹配、则返回 INVALID_GPIO_INPs、这两个引脚都为高电平或都为低电平。 这种方法可以轻松地通过 if / else 逻辑测试不同的路径、而无需对固件进行任何更改。

我已经使用编译器版本20.5和 CCS 版本12以及编译器版本22.6测试了 CCS 版本10.4的行为。 结果相同。 注意:结果随工程编译器优化级别的变化而变化。 此处列出的结果为优化级别1:局部优化。

对于所有演示板、3个测试用例的输出如下所示:

GPIO52=1、GPIO67=0:正确、如果执行、结果为:VALICE_SAFLE_0、TEST_DONE

GPIO52=0、GPIO67=1执行时出现故障、结果为:VALICAL_case1、VALICE_case_0、TEST_DONE

GPIO52=1、GPIO67=1如果执行时出现故障、结果为:INVALID_GPIO_INPINPINPINPs、VALID_C壳 体0、TEST_DONE

在所有3种情况下、第一个报告的 if case 是正确的、但当执行时显然有故障时、在程序完全退出 if / else case 之前、第二个 if /else case 的断点也会被命中。

我测试了一个假设、即当 asm (" :)语句是 if / else 情况中的最后一个语句。 在测试程序中、我将 asm (*)语句移动到每个 if / else 情况下最后一个可执行行的上方。 现在、DSS 针对所有3个测试用例正确执行调试会话。 因此、如果 if / else 逻辑是 if 或 else 情况下的最后一条语句、C2000编译器错误可能会将断点标签放置在错误的位置。 了解问题后的解决方法是移动断点标签、使其不是 if 或 else 情况下的最后一条语句。

这是一个包含 CCS 项目的 ZIP 文件。 DSS 脚本位于文件夹 JVScript 中。