请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:LAUNCHXL-F28379D 您好!

我正在尝试将我的 launchpad 与 Wiznet W5100芯片进行通信、我注意到了一些奇怪的事情。 在我的应用中、我尝试每秒读取一个字节。 为了读取它、我必须发送运算代码寄存器和虚拟数据以将我的数据推入读取。

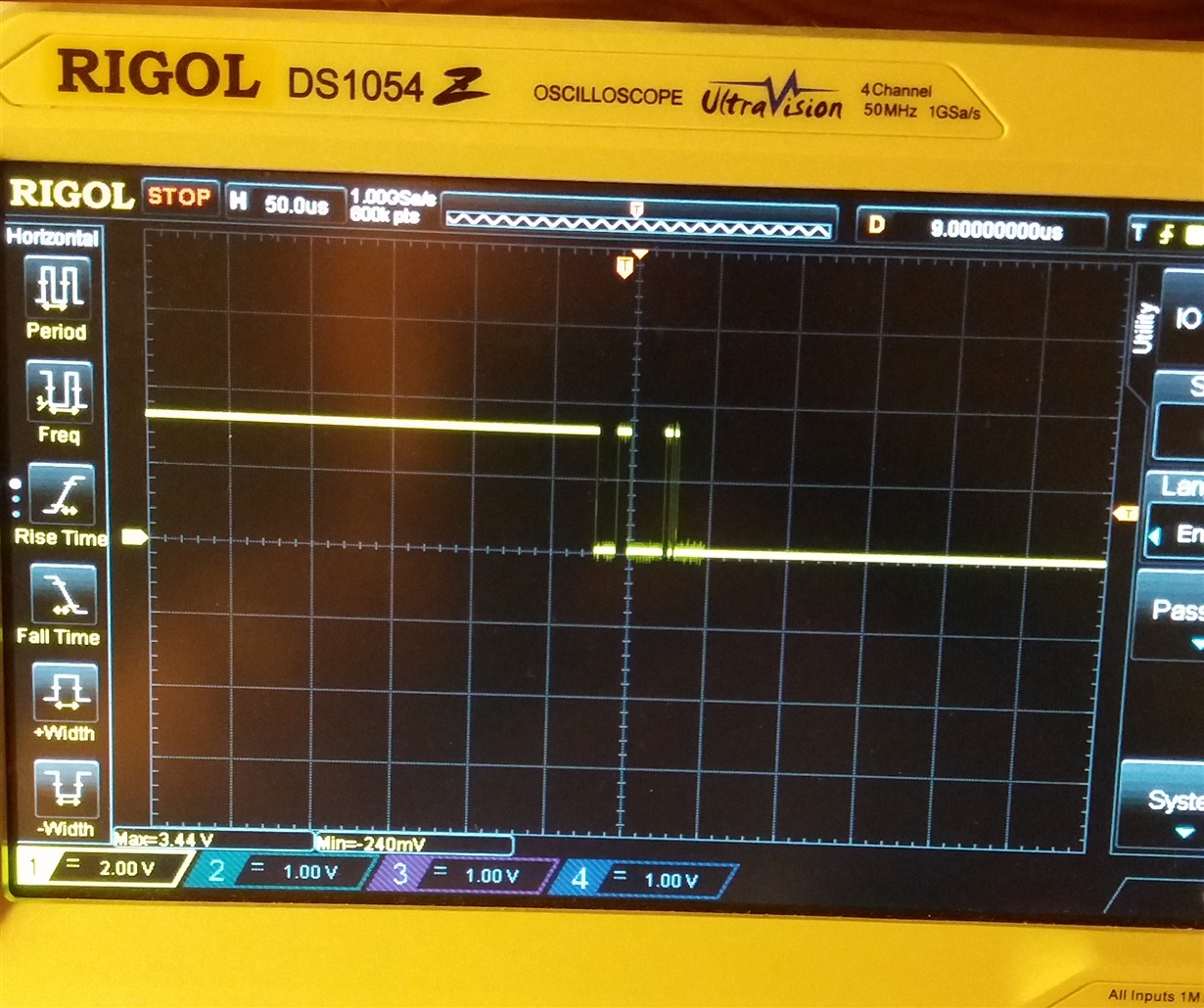

它与 MOSI 行为有关。 它不会在每次传输时恢复到高电平、我认为这是我读取的数据并非总是正确的原因。 以下是我的示波器图片:

500ms/div:

使用50us/div:

您可以看到数据已发送、但我不知道 MOSI 为何在传输后不会返回空闲状态。 以下是我初始化 SPI 的代码(来自用于 c28xx 的 TI EtherCAT hal)和用于发送数据的代码:

#include "F28x_Project.h"

#include "driverlib.h"

#include "device.h"

#include "PinMux/pinmux.h"

#if CPU_FRQ_200MHz

#define SPI_BRR ((200E6 / 4)/ 500E3)- 1

#endif

//

函数原型

//

void InitSpiAGpioPullUps (void);

void ESC_initSPIFO (void);

void ESC_writeSPI (void);

uint16_t readval[8];

volatile Spi_regs * Spixs (

void)*= 1 / void (void)。

初始化系统控制:

// PLL、看门狗、启用外设时钟

//此示例函数位于 F2837xD_sysctrl.c 文件中。

//

InitSysCtrl();

//

步骤2。 初始化 GPIO:

//此示例函数位于 F2837xD_GPIO.c 文件中,

//说明了如何将 GPIO 设置为其默认状态。

//仅为 SPI-A 功能设置 GP I/O

//此函数可在 F2837xD_SPI.c

中找到//

GPIO_setPinMuxConfig ();

InitSpiAGpioPullUps ();

//

步骤3。 清除所有中断:

//

DINT;

//

初始化 PIE 控制寄存器到其默认状态。

//默认状态是禁用所有 PIE _interrupts 并

清除标志//。

//此函数位于 F2837xD_PIECTRL.c 文件中。

//

InitPieCtrl();

//

禁用 CPU __interrupts 并清除所有 CPU __interrupt 标志:

//

IER = 0x0000;

IFR = 0x0000;

//

使用指向 shell 中断

//服务例程(ISR)的指针初始化 PIE 矢量表。

//这将填充整个表,即使在

本示例中未使用__interrupt //也是如此。 这对于调试很有用。

//可以在 F2837xD_DefaultIsr.c 中找到 shell ISR 例程

//此函数可在 F2837xD_PieVect.c 中找到

//

InitPieVectTable ();

//

//步骤4。 初始化设备外设:

//

ESC_initSPIFO ();

//

//步骤5。 用户特定代码:

//

SpixRegs->SPITXBUF =(0xF000);//重置 W5100

SpixRegs->SPITXBUF =(0x0080);

while (SpixRegs->SPIFFRX.bit.RXFFST < 2);

readval[0]= SpixRegs->SPIREXBUF =(

1)

;{advxRXBUF = 1;[pixRegs->SPIFR4]=SPIWR16];[bul_4;[bacuF = 1;[pixeIWR16]=SPIruF = 1;[bul_0]=SPIr0]=SPIr0

ESC_writeSPI ();//读取采样寄存器

DELAY_US (1000*1000);

}

空 InitSpiAGpioPullUps (空)

{

EALLOW;

//在 SPISIMO/SPISOMI/SPICLK/SPISTE 引脚上启用上拉

GpioCtrlRegs.GPBPUD.bit.GPIO58 = 0;

GpioCtrlRegs.GPBPUD.bit.GPIO59=0;

GpioCtrlRegs.GPBPUD.bit.GPIO60=0;

GpioCtrlRegs.GPBPUD.bit.GPIO61=0;

//将 SPISIMO/SPISOMI/SPICLK 引脚启用为异步

GpioCtrlRegs.GPBQSEL2.bit.GPIO58 = 0b11;

GpioCtrlRegs.GPBQSEL2.bit.GPIO59 = 0b11;

GpioCtrlRegs.GPBQSEL2.bit.GPIO60 = 0b11;

GpioCtrlRegs.GPBQSEL2.bit.GPIO61 = 0b11;

EDIS;

}

void ESC_initSPIFO (void)

{

uint16_t m;

EALLOW;

// FIFO 配置

SpixRegs->SPIFFCT.all=0x0; //将 SPI 置于复位状态

for (m=0;m<3;m++);

SpixRegs->SPIFFRX.All=0x2040; //启用 RX FIFO,清除 FIFO 内部

SpixRegs->SPIFFRX.bit.RXFFIL = 16; //设置 RX FIFO 深度

SpixRegs->SPIFFTX.All=0xE040; //启用 FIFO、释放 TX FIFO、

// SPI 配置

SpixRegs->SPIFFTX.bit.TXFFIL = 16; //设置 TX FIFO 级别

SpixRegs->SPICCR.bit.SPICHAR = 16-1; //字符长度= 8

SpixRegs->SPICCR.bit.CLKPOLARITY = 0;//上升沿

SpixRegs->SPICTL.bit.SPIINTENA=1; //已启用

SpixRegs->SPICTL.bit.TALK = 1; //

SpixRegs->SPICTL.bit.master_slave = 1;//主模式

SpixRegs->SPICTL.bit.CLK_PHASE = 1; //添加 Clk wrt SPISTEA 的1/2周期延迟

SpixRegs->SPICTL.bit.OVERRUNINTENA=1;//溢出中断被启用

SpixRegs->SPISTS.All=0x0000; //清除状态位(TxBufFull、INT、溢出)

SpixRegs->SPIBRR.all = 0x63; // LSPCLK/100

//ClkCfgRegs.LOSPP.ALL = 0x1; // 0 = SYSCLK/1 = 200M;1 = SYSCLK/2 = 100M

//SpixRegs->SPIBRR.All=0x001; //波特率= LSPCLK /(SPIBRR+1)[LSPCLK=SYSCLK/4、默认情况下=50m]

SpixRegs->SPIFFCT.all=0x00;

SpixRegs->SPIPRI.All=0x0020; //在 EMUStop 上完成事务后停止

SpixRegs->SPIFFTX.bit.TXFFIENA=0; //禁用 TXFF INT

SpixRegs->SPIFFRX.bit.RXFFIENA=0; //禁用 RXFF INT

SpixRegs->SPICCR.bit.SPISWRESET=1; //启用 SPI

EDIS;

}

void ESC_writeSPI (void)

{

SpixRegs->SPITXBUF =(0x0F00);

SpixRegs->SPITXBUF =(0x1A00);

while (SpixRegs->SPIFFRX.bit.RXFFST < 2);

readval[2]= SpixRegs->SPIRXBUF;

readval[3]= SpixRegs->SPIRXBUF;

SpixRegs->SPIFFTX.bit.TXFIFO=0; //重置 Tx FIFO

SpixRegs->SPIFFRX.bit.RXFIFORESET = 0;//复位 FIFO 指针

DELAY_US (2);

SpixRegs->SPIFFTX.bit.TXFIFO=1; //重置 Tx FIFO

SpixRegs->SPIFFRX.bit.RXFIFORESET = 1;//重新启用 FIFO 操作

}

我认为这不是 MOSI 的常规行为。 我感谢你的任何帮助。

此致、

Dawid。