主题中讨论的其他器件:SysConfig、 C2000WARE、

您好专家

我想 使用 CLB 块来控制电机换向、使用3个霍尔输入和少量其他输入来生成6个输出。

为此,我想使用每个逻辑块中的3个 LUT 和3个 OUTLUT (2个逻辑块)

请帮助我如何将 GPIO 输入映射到 CLB 以及如何将 CLB 的输出捕获到 GPIO

谢谢、此致

K.Aravind

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好专家

我想 使用 CLB 块来控制电机换向、使用3个霍尔输入和少量其他输入来生成6个输出。

为此,我想使用每个逻辑块中的3个 LUT 和3个 OUTLUT (2个逻辑块)

请帮助我如何将 GPIO 输入映射到 CLB 以及如何将 CLB 的输出捕获到 GPIO

谢谢、此致

K.Aravind

尊敬的 Aravind:

我们在 C2000 Academy 中关于 CLB 的章节很好地介绍了如何将 GPIO 路由到 CLB 模块的内部( https://dev.ti.com/tirex/global?id=c2000Academy )。 本质上、您将需要使用 SysConfig 中的 CLB 项(与逻辑块项相反)。 然后、您可以选择要进入 CLB 的输入数量以及这些输入的来源(全局或本地输入总线或 GPREG)。 回答正确、每个 CLB 逻辑块在单个配置上最多只能有8个输入

此致、

彼得

尊敬的 Aravind:

是的、我们有很多有关 CLB 的资源。 请查看位于 C2000 Academy: https://dev.ti.com/tirex/global?id=c2000Academy 的 CLB 培训模块 。 在该模块的底部、您将找到其他资源的链接、这些资源详细介绍了 CLB 和 CLB 配置。 最后、您可以完成 C2000 Academy 中的 CLB 实验、这是创建使用 CLB 模块的项目的分步过程

此致、

彼得

Peter、您好!

感谢您的答复。

我已经从以下路径 C:\ti\cc2000\C2000Ware_4_03_00_00\driverlib\f2838x\examples\C28x\ccs\clb_EX8_external_signal_and_gate 中学习了示例代码。 我已通过以下方式了解 CLB

1.我们有8个用于 tms320f28386d 的 CLB 逻辑块

2.每个 CLB 具有3个4输入 LUT 和3个 FSM 以及3个计数器和8个 OUTLUT,我们可以在 CLB 中将它们相互连接。

每个 CLB 可以有8个输入和8个输出。

我有以下疑问

1.在上面提到的示例中、两个信号都来自外部 GPIO、GPIO 如何映射到 CLB 以及在何处建立连接。 如何确认 GPIO 与 BOUNDARY IN0和 BOUNDARY IN1连接。 我缺少外部引脚与 CLB 的连接。

2.它提到我们可以从 outputxbar 获取 CLB 输出、但 outputxVBAR 只能驱动8个输出。 在这种情况下、使用 CLB、我们只能将8个输出 带到外部引脚、或者我们可以将8个以上的输出带到外部引脚。 如果我们能够获取8个以上的输出、这是怎样的可能。

期待您的回复

谢谢。

Aravind.

尊敬的 Aravind:

您对 CLB 模块结构的初始理解是正确的。 要回答您的问题、请执行以下操作:

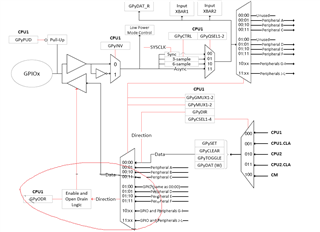

1.如果您使用 SysConfig、则可以在 Control 部分下的 CLB 菜单中完成 GPIO 到 CLB 的分配

这会配置特定 CLB 逻辑块的边界输入、然后该逻辑块通过调用 initTileX (CLBX_BASE)函数与可配置逻辑块选项中创建的配置相关联。

2.您是正确的、您受到 CLB 逻辑块上 CLB 输出数量的限制、最多为8个。 请注意、这些信号都是被复制的、因此除了用于外部引脚外、它们还可以直接转至器件上的其他外设、请查看 TRM 以了解有关该信号的详细表。

此致、

彼得

尊敬的 Aravind:

您是正确的、3类 CLB 可以从这两个引脚获取输出、 输出_交叉开关 和 CLB_OutputXBAR 。 输出_交叉开关 仍然保持了限制、即它仅有权访问每个 CLB 逻辑块的输出4和5、但 CLB_outputXBAR 可以访问任何 CLB 逻辑块输出。 有8个 OUTPUT_XBAR 和8个 CLB_outputXBAR。

因此、对于两个 CLB 逻辑块、您可以使用 output_XBAR (TILE1_out4、TILE1_Out5、TILE2_out4和 TILE2_Out5)输出4个输出。 器件上有8个 clb_outputXBAR、因此您可以输出另外8个信号。 这仅为两个逻辑块为 GPIO 提供了总计12个输出信号。 然后、您有4个剩余的 output_XBAR、因此您可以从剩余6个逻辑块中的任何一个输出4个信号(只要这些输出分配给其各自逻辑块的输出4和5)

总之、对于所使用的 x 个 CLB 逻辑块、最大输出信号数量如下:

1个 CLB 逻辑块->共8个输出信号

2个 CLB 逻辑块->共12个输出信号

3个 CLB 逻辑块->共14个输出信号

4个 CLB 逻辑块->共16个输出信号

5个 CLB 逻辑块->共16个输出信号

6个 CLB 逻辑块->共16个输出信号

7个 CLB 逻辑块->共16个输出信号

8个 CLB 逻辑块->共16个输出信号

这假设您没有为任何其他外设使用 OUTPUT_XBAR

此致、

彼得

Peter、您好!

非常感谢酒店员工的热情好客。

现在我正在处理 OUTPUTXBAR、我可以控制 为 OUTPUTXBAR 选择的 GPIO 来启用或禁用吗?

参考上面的图表(参考手册中的第1547页)、我在这里画了一个红圈。

多路复用器的输入全部外设、GPIO、 OUTPUTXbar 在此丢失。

1)配置为 OUTPUTxbar 的 GPIO 是否默认选择为输出并在上电后驱动为默认值?

如果需要、我可以随时使用其他寄存器来禁用或启用为 OUTPUTXBAR 配置的 GPIO。

谢谢。

K. Aravind.

尊敬的 Aravind:

有关 OUTPUTXBAR 如何连接到 GPIO 的示意图、请参阅 XBAR 一章。

在启用或禁用为 OUTPUTXBAR 配置的 GPIO 方面、您可以利用 OUTPUTxMUXENABLE 寄存器在任何时间点启用和禁用 OUTPUTXBAR。 通常、在代码中配置 GPIO 后、GPIO 将从关联的 OUTPUTXBAR 输出、尽管由于您使用的是 CLB、您也可以选择在要激活输出的时间点通过调用 CLB_enableCLB 函数来启用 OUTPUTXBAR 输出。 尽管这适用于连接到逻辑块的所有 OUTPUTXBAR

此致、

彼得