在 TRM 中、表32-1显示 CLB 逻辑块时钟是同步模式下的 SYSCLK。 但在图32-3中、CLB 逻辑块时钟是由 PERCLKDIVSEL.EPWMCLKDIV 决定的 SYSCLK 的分频时钟。

以下哪项陈述是正确的?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

在 TRM 中、表32-1显示 CLB 逻辑块时钟是同步模式下的 SYSCLK。 但在图32-3中、CLB 逻辑块时钟是由 PERCLKDIVSEL.EPWMCLKDIV 决定的 SYSCLK 的分频时钟。

以下哪项陈述是正确的?

更多内容。

F28003x 是否如图32-3所示具有 AUXPLL? 是 CLBCLKCTL。 CLBCLKDIV 和 CLBCLKCTL。 TILECLKDIV 寄存器有效吗?

我在 F28003x 的数据表和 TRM 中找不到 AUXPLL 的任何说明。 是 PLLRAWCLK 吗?

2.如果 CLB 在 AUXPLL 中工作,它将与 SYSCLK 中的其他模块异步。 许多来自 SYSCLK 的 CLB GLB/LCL 输入、CLB 是否可以正常工作?

从图3-3中、CLB 在 SYSCLK 中工作、这与图32-3中的描述相矛盾

1.我无法理解这张图、从 TRM.table 3-47来看、用于控制 SYSCLK 源的 SYSPLLCTL1来自 pllrawclk 或 OSCCLK。

所以图中 SYSPLLCTL1的输出是 SYSCLK? 而 CLB 时钟源仅是 SYSCLK?

2.但来自 TRM。 FIGURE32-3和您的回复、我想 clb.tileclk/regclk 源是 AUXPLL(PLLRAWCLK??)的 SYSCLK。 由 CLBCLKCTL.CLKMODECLBx 控制。

1和2个结论相互矛盾。

3.如果 CLB 可以使用 SYSCLK 在异步时钟下工作,此配置上是否有任何应用程序? 由于其他模块在 SYSCLK 中工作(如 EPWM/eQEP/ECAP/SPI/FSI/LIN/SCI、基于 TBale32-4和 PIE)、在 SYSCLK 下工作的模块可以捕获 CLB 输出?(例如、 ) CLB 时钟在120MHz 为 PLLrawCLK 而在10MHz 为 SYSCLK 为 OSCCLK、则如果 CLB 产生中断、在 SYSCLK 上工作的 PIE 模块可以接收此中断吗?Δ t

尊敬的 Liu、

当 SYSPLLCTL1.PLLCLKEN 和 SYSPLLCTL1.PLLEN 都设置为1时、PLLRAWCLK 将用作 SYSCLK 和 CLB 时钟的源时钟。

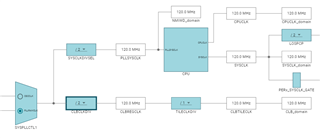

2.此图不正确。 正确的图位于时钟树工具中:

我已提交一个 TT 以在 TRM 中更正此问题。

3.如果 CLB 时钟和 SYSCLOCK 具有相同的频率、则不认为有任何用例使 CLB 时钟与 SYSCLK 异步。

谢谢!

卢克

1.根据您的解释,我能不能认为 CLB.CLKCTL.CLKMODECLBx 没有任何用途?

a. CLB 逻辑块时钟由 CLBCLKCTL 确定。 TILECLKDIV

b:CLB reg clk 由 CLBCLKCTL 确定。 CLKDIV

2.那表32-1怎么样呢? 是这样吗?

3.如果我运行 CLB。 60MHz 和 SYSCLK 中的寄存器/逻辑块位于120MHz 中,CLB 在 SYSCLK 中接收信号是否存在任何问题(例如 ERAD_evtx)?

4.是否存在 CLB 使用 SYSCLK 以不同频率工作的任何应用?