Thread 中讨论的其他器件:LMK05318B、 LMK5C23208A、 LMK5B12212

工具/软件:

您好:

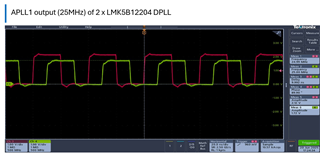

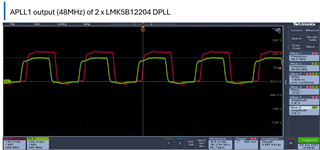

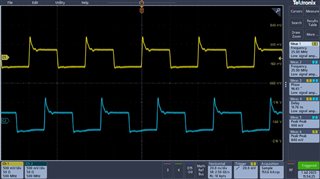

我们使用提到的 DPLL 部分作为时钟发生器、从 APLL1 和 APLL2 输出生成不同的频率。 APLL1 将是 48MHz、APLL2 将是 25MHz。

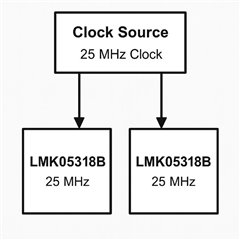

要求我们有多个 DPLL 芯片、每个芯片都能同步生成上述频率。 25MHz 或 125MHz 时钟将连接到 DPLL 的 PRIREF 输入、25MHz 振荡器将连接到 XO 输入。 我们要求多个 DPLL APPL1 输出应相互同步、对于 APLL2 来说也是如此。

请告知我们使用此器件是否可以实现/可行?

此外、是否有办法通过 PRIREF 输入时钟修复 APLL1 和 APLL2 输出的相位延迟?

谢谢!