尊敬的 Derek Payne / https://e2e.ti.com/members/1885803 / Team

我们将 LMK04828用于 PLL2模式下的 RFSoC

我们将馈送 OSCIN 100MHz (标准振荡器、即、不是 VCXO)

振荡器部件: Si545

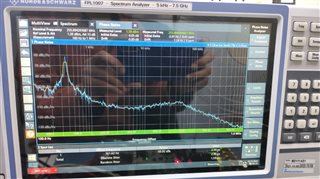

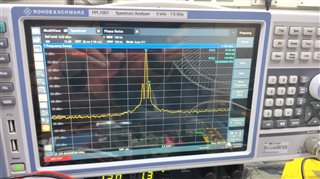

我们将在 LMK 和射频输出处观察输出频率漂移/抖动超过200Hz。

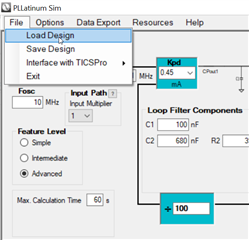

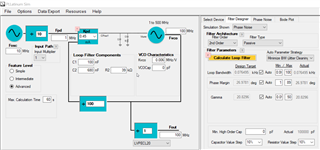

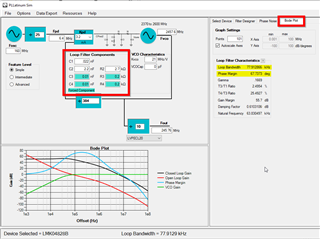

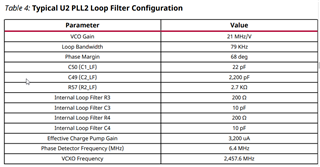

PLL2外部环路滤波器:

下面是根据原理图对滤波器进行的 Platinum 仿真

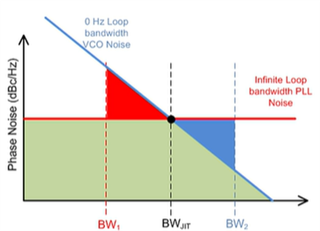

我们如何最大限度地减小频率漂移?

是否应改变 PLL2的内部环路滤波器或外部滤波器以避免频率漂移?

请建议。

由于我们仅使用 PLL2、因此优化抖动的 PLL BW 应该是多少?

为了实现优化的性能、应该有什么相位裕度?

为了 优化性能、开环和闭环增益应该是多少?

谢谢。

\

\