Other Parts Discussed in Thread: AFE5816, AFE5816EVM

工具与软件:

大家好!

我正在使用 AFE5816器件开发医疗超声波系统。 我需要使用 AFE5816将接收到的信号数字化、我对数据表中所述的时钟要求有疑问。

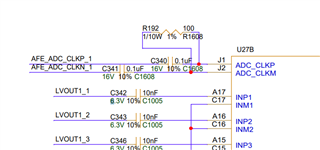

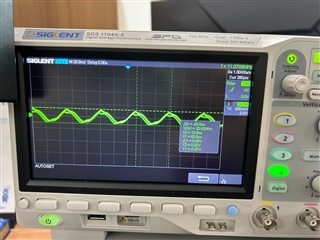

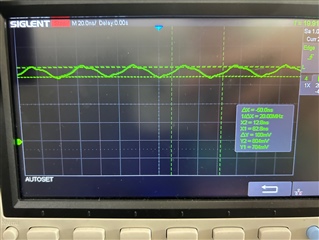

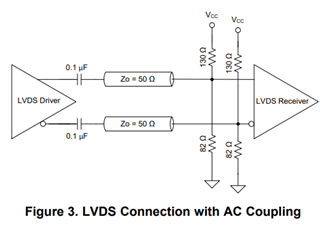

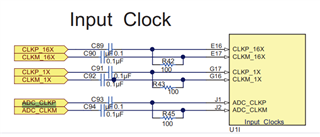

我计划使用 LVDS 或 LVPECL、当交流耦合时、时钟要求提到 Vpp 值、而共模电压在内部设置为1V。 我的电路板提供的时钟如下图所示。 即使满足 Vpp、但它不是交流耦合、是否会出现问题?

另外、您能告诉我 LVDS 和 LVCEPL 中正常运行情况下的 Vpp 最小值吗?

在数据表中、有一个典型值。

谢谢你