主题中讨论的其他器件: TPS2556、 TPS25750、 TPS25751

工具/软件:

您好:

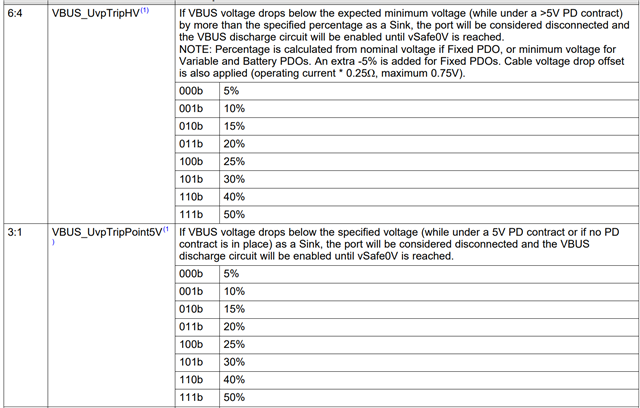

我正在寻找 TPS65987DDK 的 UVP 跳闸设置。

根据 DDH 的技术参考手册、有以下设置。

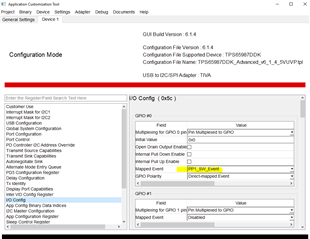

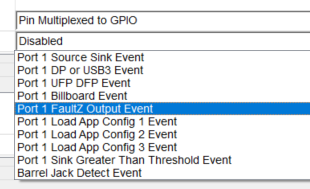

因此、我选中了应用程序自定义工具、它只有以下设置项。

*"欠压保护使用 PP_HV

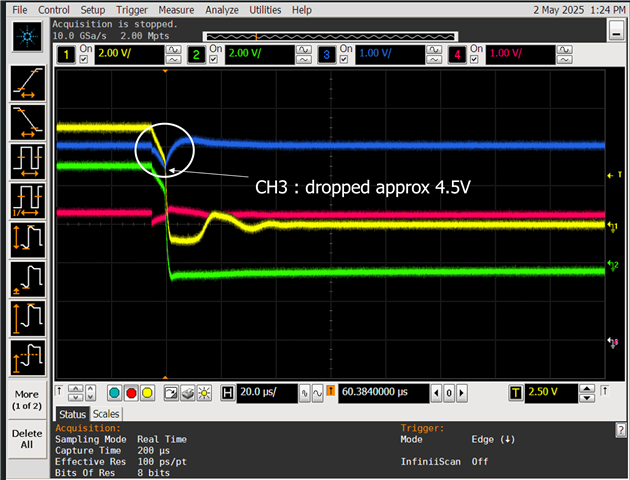

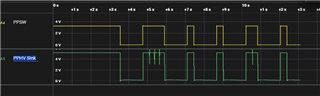

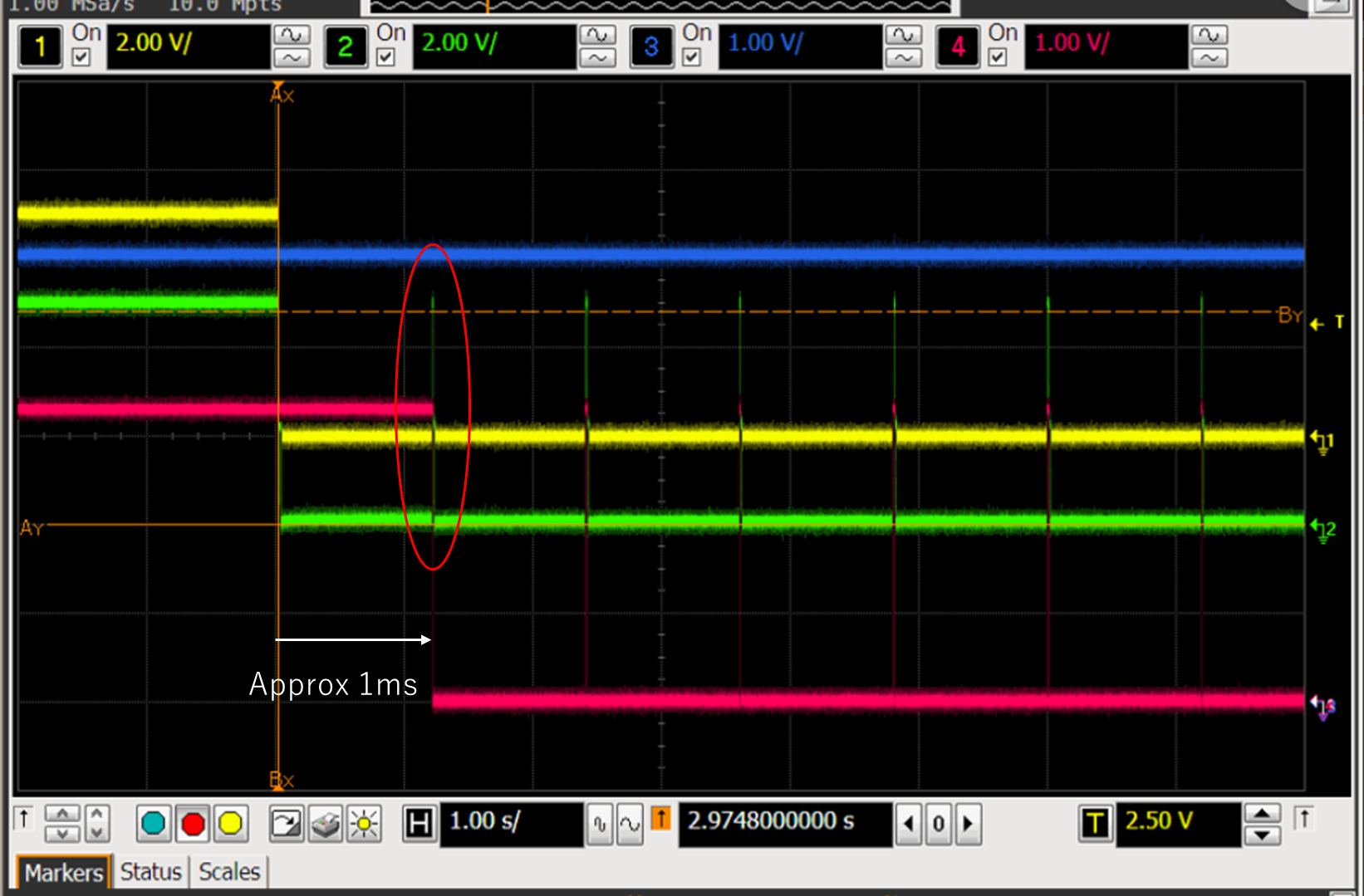

我尝试更改该值、但似乎 bitfield [6:4]已更改。 我使用的是固定5V/3A DFP。

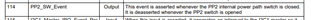

因此、我想确认用户如何更改 bitfield [3:1]内容。

您是否有任何关于 TPS65987DDK 的"vbus_UvpTripPoint5V"的信息以及我们如何更改该值?

此致、