工具/软件:

尊敬的 TI 团队:

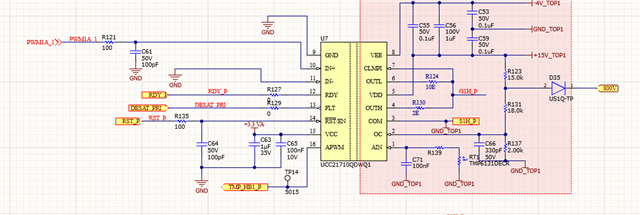

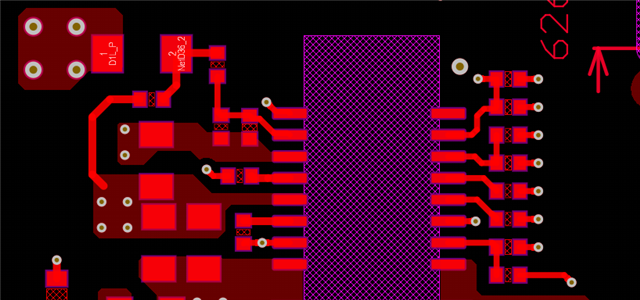

此栅极驱动器 (UCC21710-Q1) 有一个问题、因为当我将栅极驱动器开关到 100V 以上时、我使用栅极驱动器为 1200V MOSFET (AIMCQ120R030M1TXTMA1) 提供栅极脉冲、我观察到栅极驱动器通过获取一些电流自动禁用。 在 100V 以下、我观察到栅极脉冲中的正弦波、我仅在高侧 MOSFET 栅极驱动器上观察到了这个现象。 因此、我禁用了 OC 引脚和 AIN 引脚(拉至 GND)、即使禁用它意味着我没有获得+!5V 和–4V 的任何脉冲。 请给出任何解决方案。 如何操作?我附加了栅极驱动器电路的原理图。