Other Parts Discussed in Thread: UCC28782, PMP22244

部件号: UCC28782

主题: PMP22244 中讨论的其他器件

尊敬的 TI 工程师:

使用 UCC28782 芯片时遇到了一些问题、想征求您的建议。

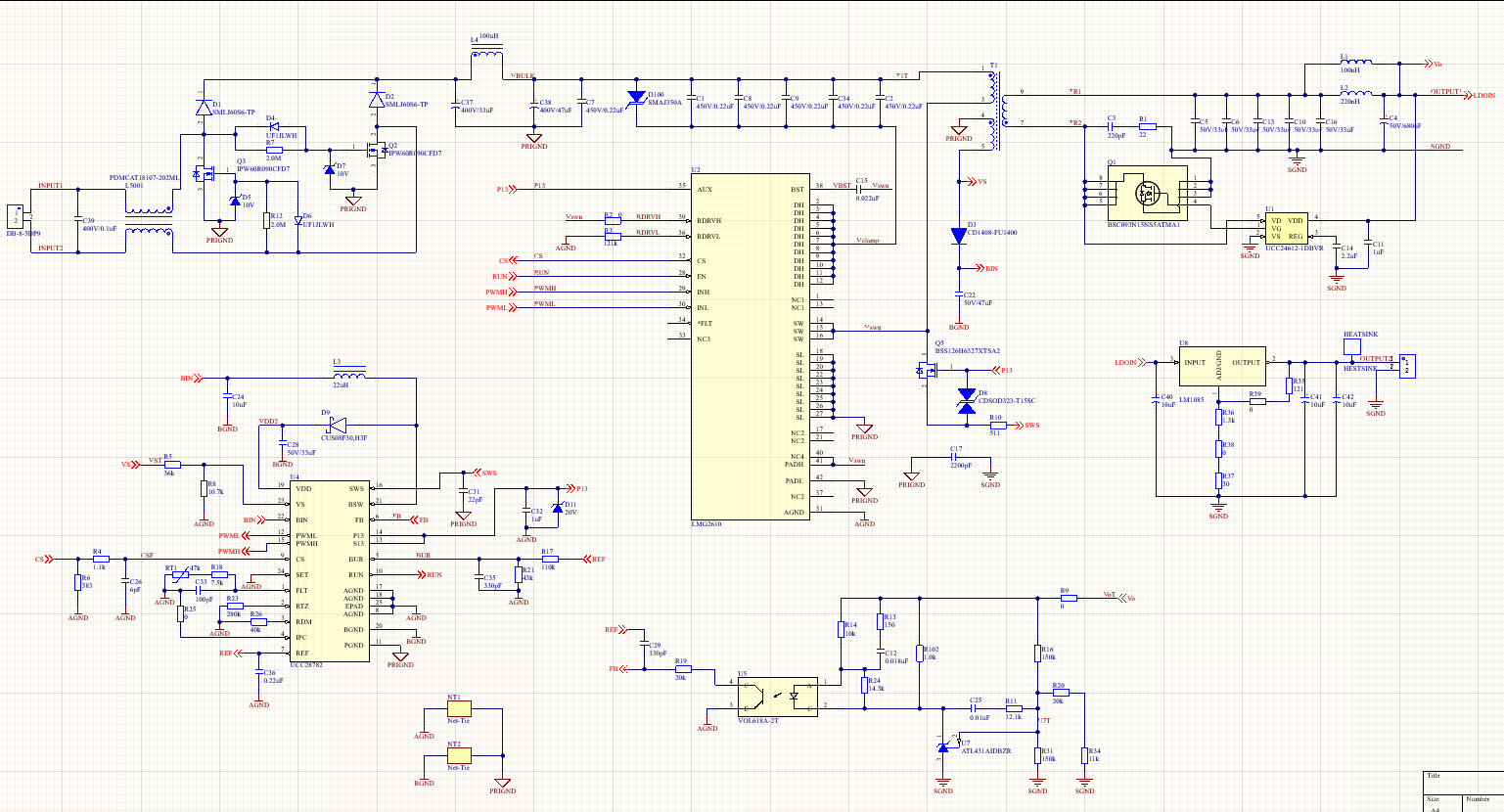

我的电流电路设计参考了 PMP22244 结构。 使用参数设计表计算特定参数后、结果如下所示、输入:220VAC 输出:17.2V/2A 变压器比率:8:1:1。

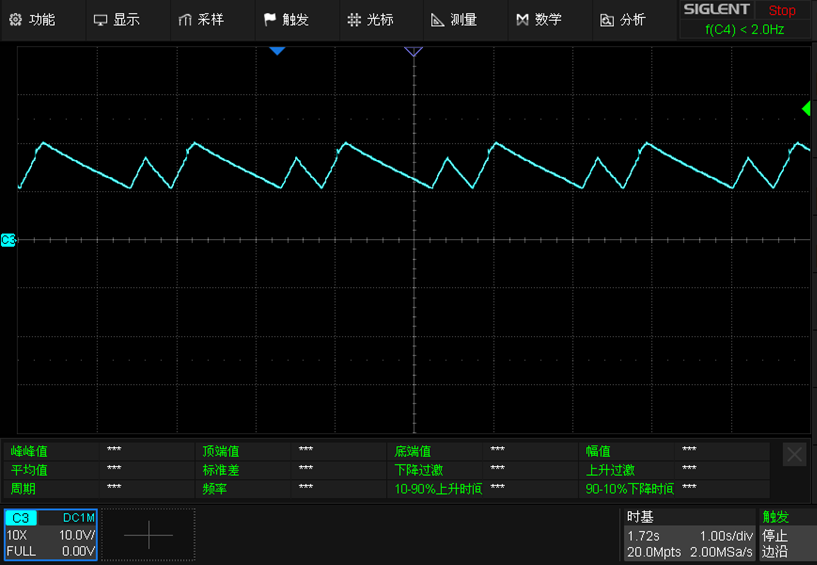

当前问题是 VDD 电压在轻负载条件下不稳定、并会反复重新启动。 如图所示、这是 220VAC 输入和 1500 Ω 负载条件下的 VDD 波形。

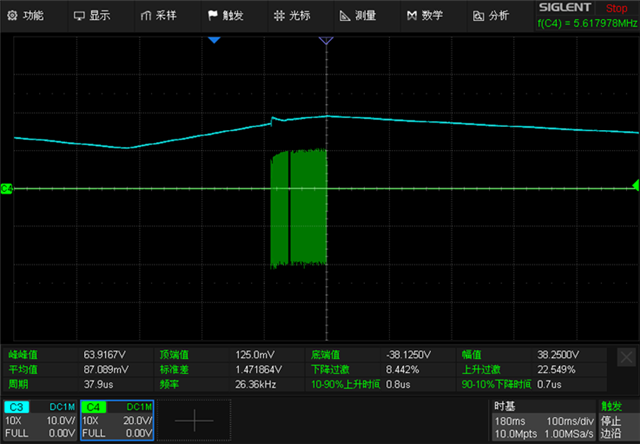

当负载电阻小于 170 欧姆时、VDD 电压保持稳定、输出也稳定。

我想问这种情况背后可能有哪些原因、以及我应该如何解决。

非常感谢。