您好的团队:

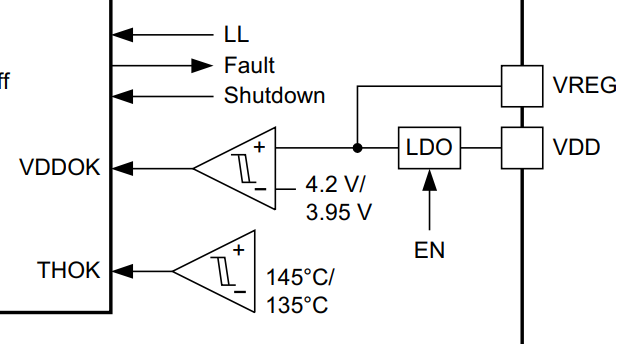

我的客户报告说、TPS53355有两个器件无法正常输出30A、仅输出21A。 但是、如果输入电压增加、输出电流能力也会增加。

异常电路板的情况如下:

1.5.5V 输入、1V 输出、估计约为21A。

2.7.5V 输入、1V 输出、估计约为27A。

但正常电路板、5.5V 输入、1V 输出、大约为27A。

我们尝试的实验:

正常输入大约为5.4V。 如果输入电压升高到大约6V、则其他条件保持不变、输出负载电流可增加约4A。

2. 第一块异常板增加了一个200uF 的输入电容、第二块异常板增加了300uF、其他条件保持不变、输出负载电流可以增加大约3A。

基本检查:

1.无虚拟焊接,无 虚假焊接。

2.使用风扇冷却。不会过热。

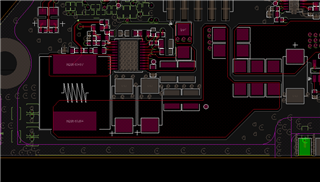

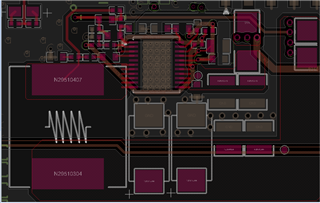

按附件的方式进行 Sch 上传。

您能帮您回顾一下这个 SCH 吗? 并确认上述2实验为何可以提高负载 能力 ?

提前通知 Tks。