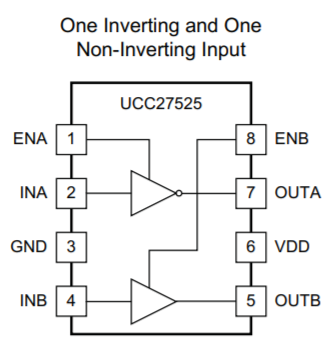

Other Parts Discussed in Thread: CSD18542KTT, UCC27511, CSD18510Q5B, CSD18536KTT, CSD18512Q5B, CSD18563Q5A, CSD19505KTT, CSD19505KCS, UCC27525

主题中讨论的其他器件: UCC27511、 CSD18510Q5B、 CSD18536KTT、 CSD18512Q5B、 CSD18563Q5A、 CSD19505KTT、 CSD19505KCS、 UCC27525

尊敬的专家:

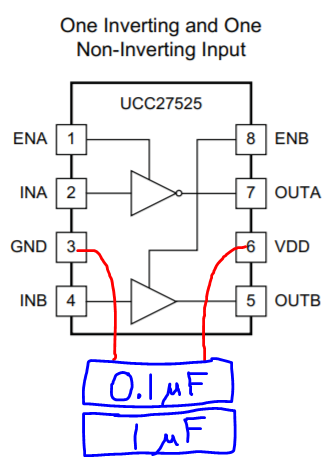

我无法在 pspice 中仿真该电路、该 MOSFET 电路是否正确、如果错误、请帮助我构建更好的电路。

CSD18542KTT