Other Parts Discussed in Thread: PMP20745, LM5022

主题中讨论的其他器件:PMP20745、

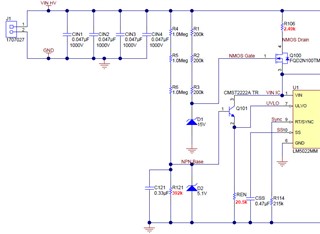

在输入开始出现时、如何计算 U1引脚1上的电压? Thiis 部分原理图是从您的参考电路 PMP20745复制的。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好、Genie、

FET Q100的工作方式与 LDO 类似、可将输入电压从电源电压下调至~ 15V (来自 D1)+来自 Q100的 V_GS。

这用于本参考设计中的输入 VIN_HV 可能高于 LM5022允许的电源电压。

我相信、作为起点、您将能够计算输入设计。

请注意:R4、R5、R6 R121、C121 Q101不会在很大程度上影响 LM5022的 VIN 电压。

此致、

Stefan

您好 Stefan、

1. LM5022的 VIN 是否等于 ~ 15V (来自 D1) -来自 Q100的 V_GS、但不等于 ~ 15V (来自 D1)+来自 Q100的 V_GS?

2. Q101的功能是什么? 根据您的状态、FET Q100 的工作方式与 LDO 类似、可降低输入电压、Q101似乎是冗余的。

R106和 REN 的功能是什么?

此致、

网件精灵

您好、Genie、

1.你在这里的位置完全正确-很好的收获-谢谢。

2.这会生成 UVLO 输入信号-此电路实现可防止 UVLO 上的信号高于 VIN 上的信号。

3. Ren 是 UVLO 的下拉电阻-因此当未通过 Q101启用时可设置适当的0V。

R106将接受部分电压、因为 FET 的额定电压仅为100V、但输入电压可高达400V。

另请参阅 PMP20745的报告(第5.1章)中的启动范围图

此致、

Stefan

您好 Stefan、

我很困惑。

1. LM5022的 VIN 等于 ~ 15V (来自 D1) -来自 Q100的 V_GS。

2. Q101的 VCE 可被视为0V (根据您上次的回复)。 因此、Q101的 Ve 等于 ~ 15V (来自 D1) -来自 Q100的 V_GS。

3. Q101的基极电压为5.1V

将1、2组合在一起、如何打开 Q101?

此致、

网件精灵