请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:TPS3840 您好!

我是 TI 产品的经销商 FAE。

我收到了一个客户关于启动行为的问题。

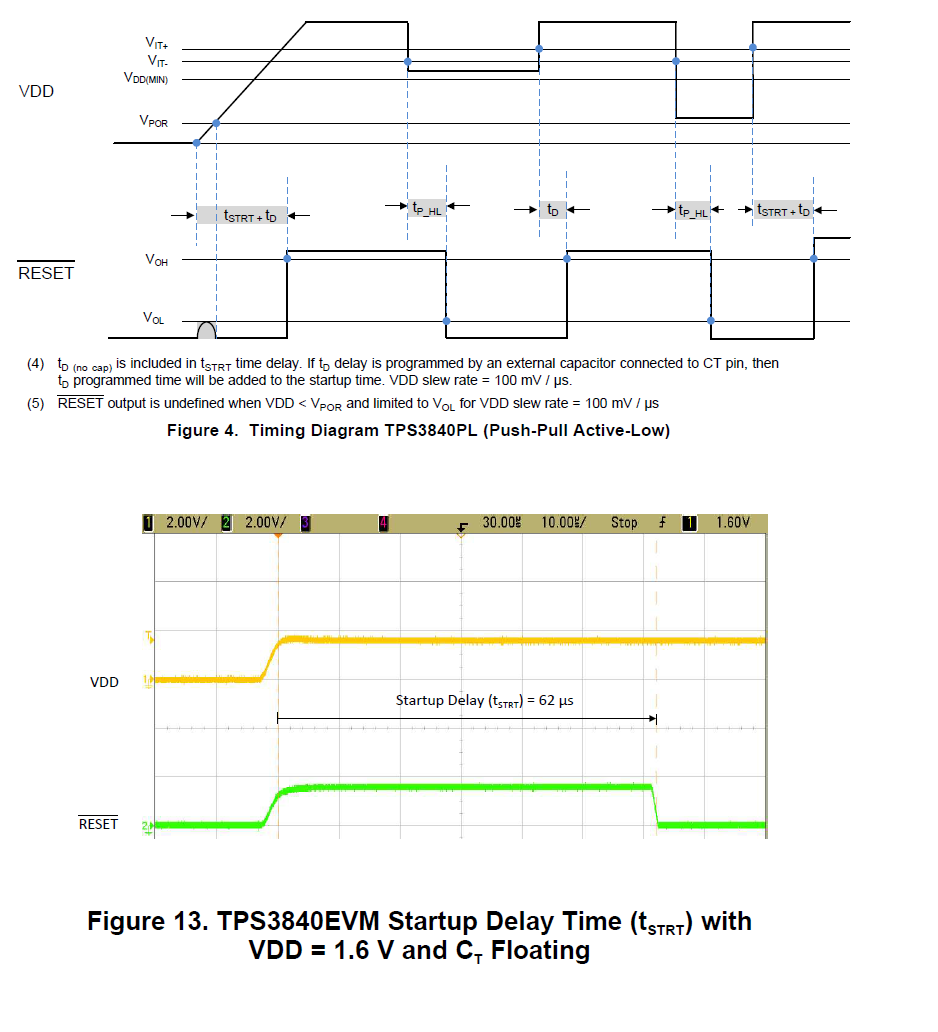

上图是数据表的摘录。 (TPS3840PL)

下图是 EVM 摘录。 (TPS3840DL)

我的客户的问题是、当 VDD 在启动时未达到 VIT +时、复位是否变为高电平。

启动时、当 VDD 介于1.6V 和 VIT +之间时、EVM 波形复位为高电平、持续62us。

这表示在启动时复位需要一些时间才能生效。

当 VDD 介于 VPOR 和1.6V 或更低之间时、是否会发生相同的行为?

我收到了一个客户关于启动行为的问题。

上图是数据表的摘录。 (TPS3840PL)

下图是 EVM 摘录。 (TPS3840DL)

我的客户的问题是、当 VDD 在启动时未达到 VIT +时、复位是否变为高电平。

启动时、当 VDD 介于1.6V 和 VIT +之间时、EVM 波形复位为高电平、持续62us。

这表示在启动时复位需要一些时间才能生效。

当 VDD 介于 VPOR 和1.6V 或更低之间时、是否会发生相同的行为?

此致、