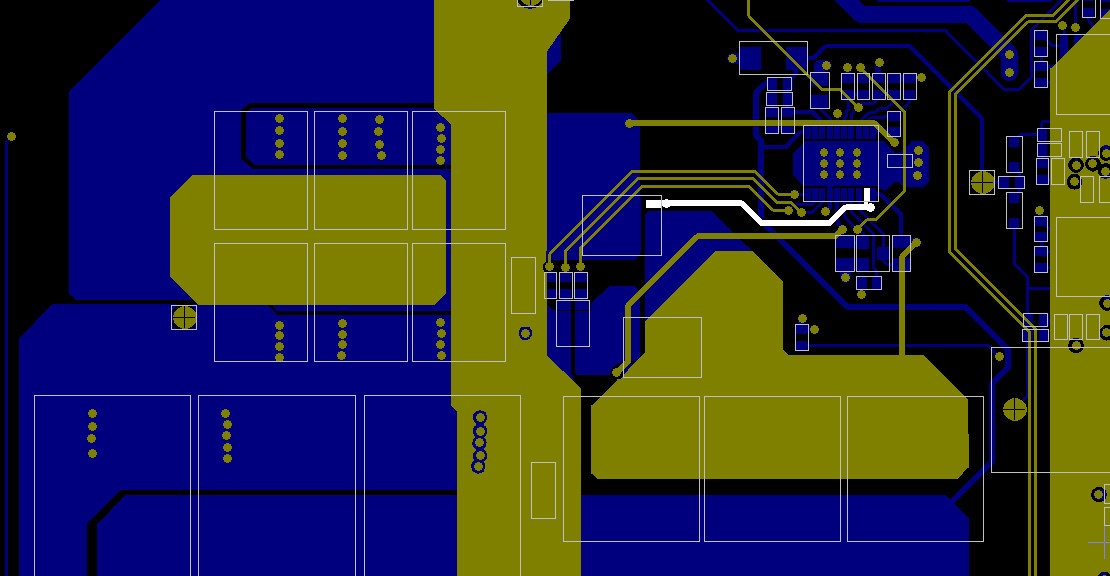

大家好、我将 LM5116用作可变输出电压直流/直流转换器。 为了设置输出电压、我将使用一个非常简单的 PID 控制器。 PID 误差的计算方法为设定点(使用 DAC 编程)减去直流/直流的电压反馈。 PID 输出连接到 LM5116的 FB 输入。 在这里 、您可以找到原理图的摘录。

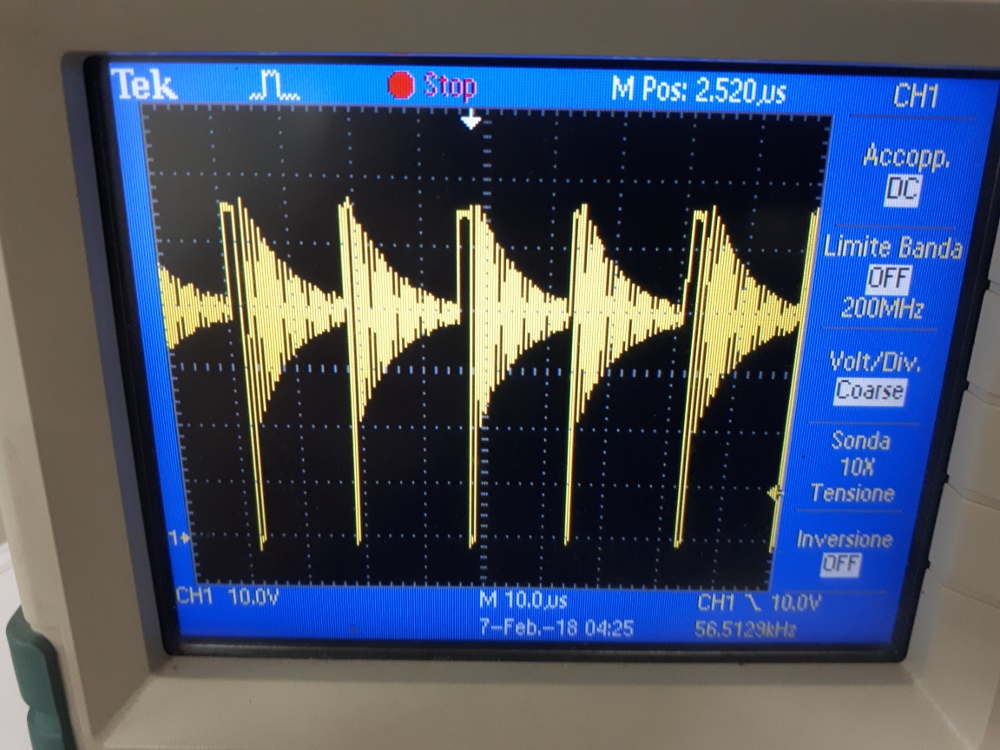

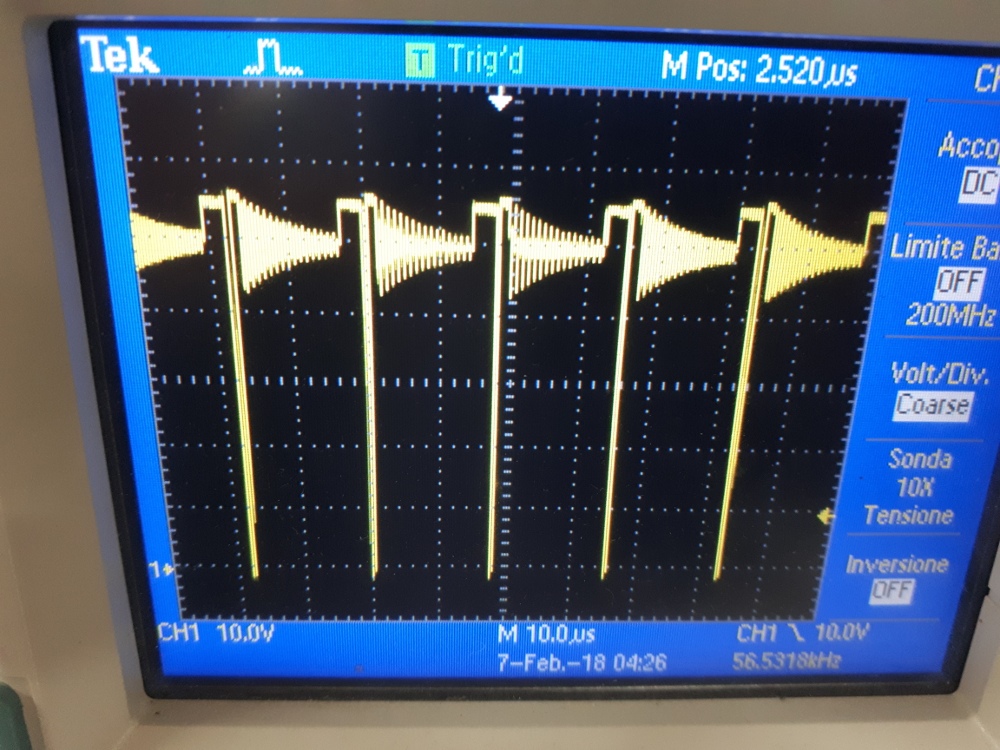

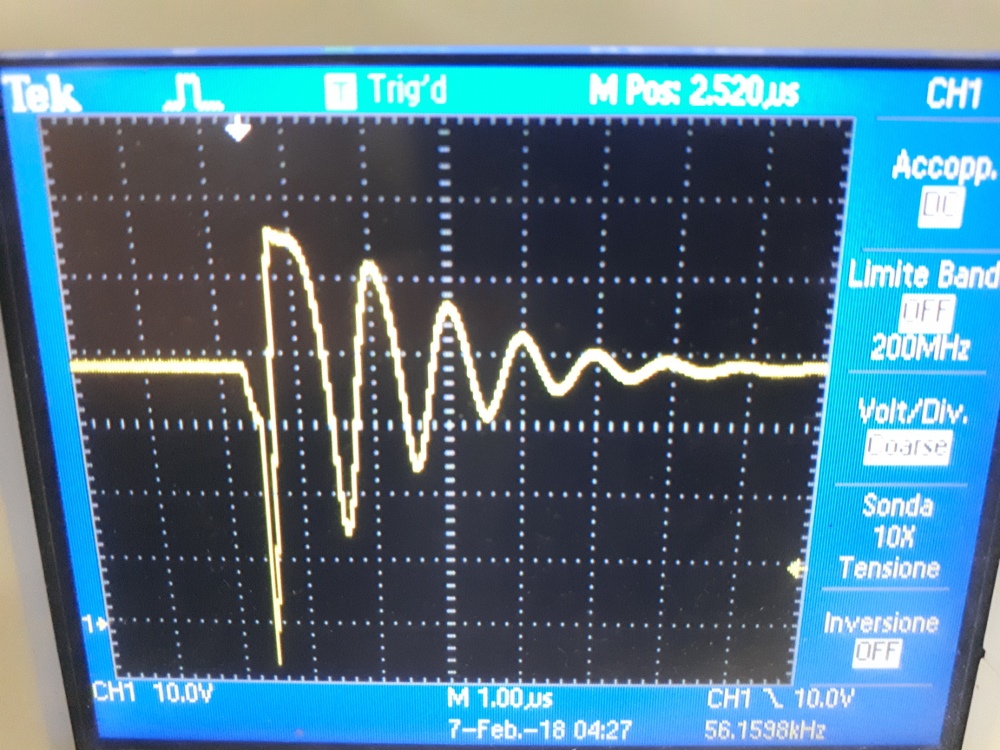

除了以下情况外、一切都正常:如果我选择一个无法达到的设定点(例如、当输入为54V 时输出为55V)、直流/直流将停止工作。 由于反馈无法达到设定点、因此 PID 输出(以及 FB 引脚)低于1.215V 并保持不变。 这似乎干扰 了 LM5116:它不是将输出设置为100%(如预期的那样)、而是明显地"冻结" PWM 占空比为一个恒定值(如果这很重要的话、大约为70-75%)、并且完全停止使用 FB 输入。 从这一刻起、输出电压会随输入电压成比例地变化。

我还尝试添加一个略低于1.215V 基准的恒定电压(请参阅原理图上红色虚线矩形内的网络)、以防出现某种" FB 欠压保护"、但未发生任何变化。

是否有办法"欺骗"LM5116 、以便在 FB<1.215V 时强制其生成最大输出电压?

P.S. 如果没有机会做到这一点、下一步将是使用 DAC 作为某种"可编程电位器"、将其基准输入与输出反馈电压进行馈送。 但是、我更喜欢一种更简单的解决方案、它不会迫使我更改固件。

谢谢!