主题中讨论的其他器件: TIDA-00778

您好!

几周前报告的情况被认为是 HB 泄漏、因为尚未安装 FET。 遗憾的是 、在安装了 HO/LO 栅极驱动器后、报告的情况仍然存在。

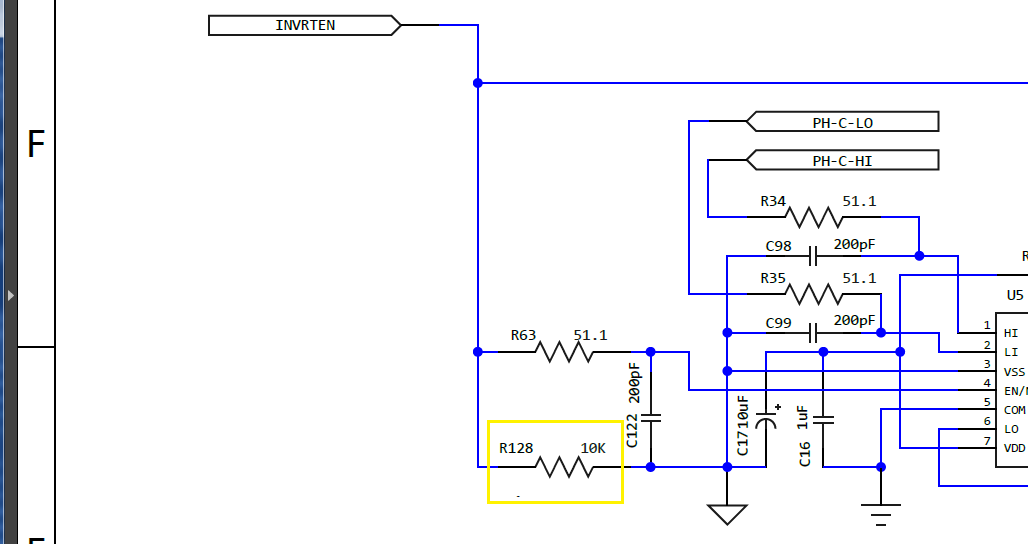

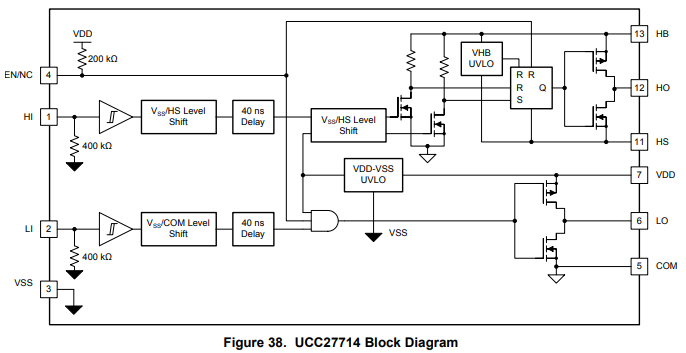

MCU PWM 引脚1/2 (下拉 20k)和 GPIO 驱动 器 EN 引脚4 至三个 uC 器 件的 POR 在 HO 变为高电平时将 EN 线下拉10k 为0V。

电源+15 VDD 具有2.97ms 的延迟、延迟高达3V3 MCU 功率捕获的80%、如下所示。 这些 uC 一直将 POR 上的 HO 设置为高电平、 并且不遵循数据表中的真值表。 确保在每个引脚上焊接烙铁温度258*C 的时间少于10秒大多数是在 不到4秒的时间内完成的,焊到焊盘 上看起来非常干净,不是很冷。 在 HS/HO 引脚11/12之间并联20k/16V 齐纳二极管、并 在任一引脚上测量+13v。

导致 HO 始终保持打开的原因 是、LO 在 POR 期间保持0v。 任何到引脚1/2的 PWM 驱动都会导致1/2电桥击穿、 同时 MCU 紧急关闭。

已向系统施加电源:HO 至 VDD 上升: