主题中讨论的其他器件:UCC28951

您好!

我正在使用 TIDA-020031参考设计设计设计相移全桥电路、其输出电压为20V、电流为150A、最大功率为3000W。

变压器匝数比为8:1、匀场电感器为7.5uH、输出电感为3.3uH、采用双倍电流整流方案。

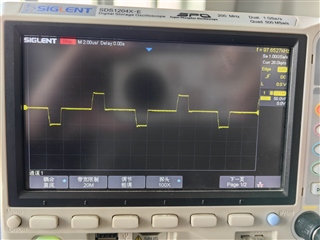

当前的问题是、当禁用 E 和 F 输出时、输出是正常的、最大电压为19V、最大电流为140A、最大功率为2700W。 然而、在启用同步整流后、输出电压不能上升、并且 A、B、C 和 D 的间歇输出也不能比较 A 和 F 之间的延迟。

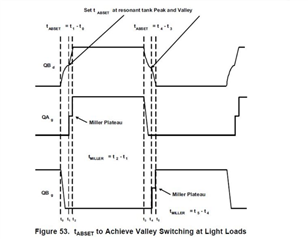

怀疑是由于 E 和 F 开始输出信号后次级侧由整流器 MOS 晶体管短路所致。 死区时间设置 Rab=RCD=13k 采用自适应死区时间、图中显示了电阻网络。 请帮我、我应该从哪个方面进行调整?