主题中讨论的其他器件: LM74502H-Q1

您好

我们 在您的系统上有 LM5060设计。

它与 lm5060数据表类似

"图28. 接通时间延长"

我们还添加了 C1、以添加开通时间延长。

通过考虑"栅极引脚"驱动 Cababilty 是否存在 C1的任何最大值。 ?

或者我们不会担心栅极引脚上的电容值(当 MOSFET SOA 足够强大时)

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好

我们 在您的系统上有 LM5060设计。

它与 lm5060数据表类似

"图28. 接通时间延长"

我们还添加了 C1、以添加开通时间延长。

通过考虑"栅极引脚"驱动 Cababilty 是否存在 C1的任何最大值。 ?

或者我们不会担心栅极引脚上的电容值(当 MOSFET SOA 足够强大时)

我们建议使用尽可能低的栅极电容、因为它会影响 LM5060的关断响应时间。

-0704-> 您是对的,我也 测量了关闭时间,以使它可以完全填充我的设计。

增加 C1的动机是什么? 它是否用于限制浪涌电流?

0704-->我的动机是限制浪涌电流。

您能否分享您的原理图、应用用例、Cout 值详细信息

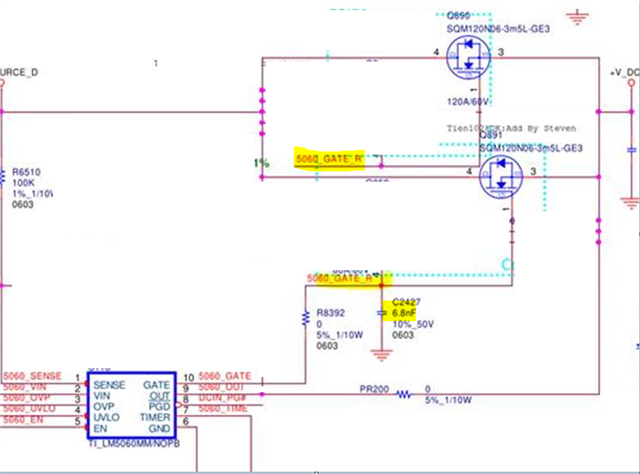

0704-->我的设计如下,C1现在是6.8nF。

请向我提供有关 C1值的建议。

感谢您的

在 FET 开启之前、VDS 应等于 VIN。 为什么当 VIN=24V 时为35V? 您能否为每个 MOSFET 添加栅极电阻器(4.7欧姆)并检查一下?

如果 FET 处于 SOA 限制范围内、则驱动电流不是问题、否则您可能需要减慢栅极的速度以减小浪涌电流(Ids)。 最坏的情况是、您需要在最高工作温度下进行检查。 此外、在关断期间检查 FET SOA 是否存在过载故障

此致、

勒凯什