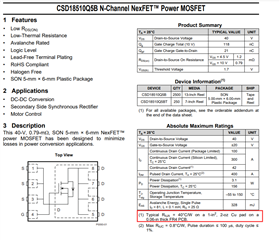

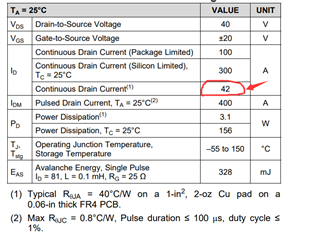

Other Parts Discussed in Thread: CSD18540Q5B, CSD19536KTT, LM74700-Q1, CSD19533Q5A, CSD18510Q5B, CSD88584Q5DC

主题中讨论的其他器件:LM74700-Q1、 CSD18510Q5B、CSD18540Q5B 、CSD19536KTT 、 CSD88584Q5DC

大家好、支持团队。

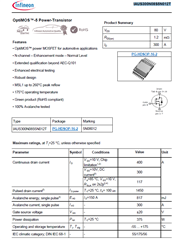

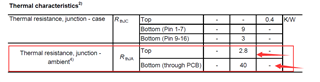

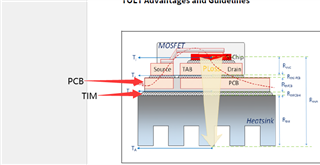

我计划使用两个 LM74700-Q1实现 ORing 功能、输入电源为直流18V~32V、常规电压为直流24V、电流为200A。 TI 是否有手册介绍在大电流下并联使用 MOS 管的球管选型方法? 例如、如果电压为24V DC、电流为200A、且工作温度为-40℃~85℃、那么 LM74700-Q1可以驱动多少个来满足这一需求?

例如、CSD19533Q5A 应使用多少个并联连接?