主题中讨论的其他器件: TPS541620、

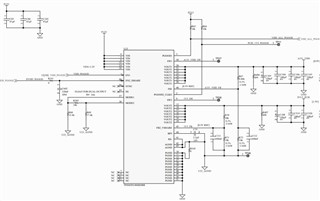

我将按照以下配置使用 TPSM5D1806:

输入电压= 12V

VOUT1 = 0.9V (3A)

VOUT2 = 1.5V (2A)

1MHz 开关频率

在0.9V 电压轨上提供500uF 的输出电容。

在1.5V 电源轨上提供300uF 的输出电容。

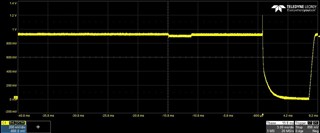

两个电源轨在加电期间都保持稳定。

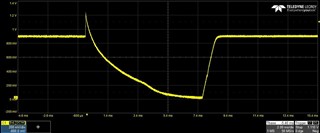

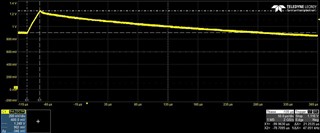

我看到在电流消耗周期内(馈入处理器的内核电压) 0.9V 电压轨尖峰(在20ms 内从0.9V 稳定上升到1.3V)。

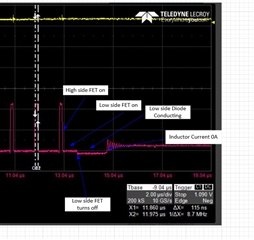

我会监控 SW1引脚、并看到在此斜升期间脉冲仍在进行(宽度逐渐减小)。 稳压器关闭然后打开。 我猜是输出上的过压导致了这种情况。

这是怎么回事????? 如果电流消耗从6A 突然变为0A、我预计由于环路响应、输出电压会短暂增加。 但是、我希望它的响应速度快于20ms。

我尝试了与上部反馈电阻器并联的前馈电容器(47pF、150pF、470pF)、但输出没有变化。

我尝试了以500kHz 的开关速率运行电源、没有实际的行为变化。

我在输出中另外增加了一个600uF 的陶瓷电容、没有变化。

我们将非常感谢您提供任何帮助。

-凯文