工具与软件:

嗨、团队:

我将设计一种半桥 PFC、

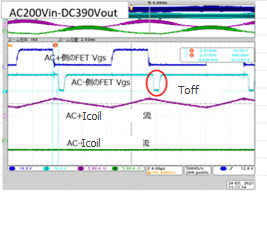

在一段时间内、当 AC+侧导通时、交流侧的 FET 关断。

是什么触发了这种情况?

与交错不同、电流方向是反向的、因此 CSx 端子卡在低电平、所以我认为无法检测到电流边沿。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi Kobayashi-San,

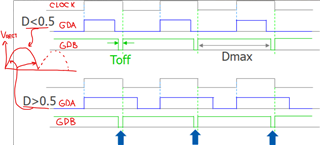

是的、Toff 时序是不可避免的。 该时序由两个栅极驱动输出的180度交错强制实施。

交错以 栅极驱动信号 GDA 和 GDB 的上升沿为基准。

关断时间为变量、从栅极驱动器的下降沿开始。

对于具有负电流(从源极到漏极)的 MOSFET、占空比始终为最大值(接近但绝不等于100%)。

在短暂的关断时间内、负电流流经 MOSFET 体二极管。 一旦 MOSFET 再次驱动、电流就会再次通过漏源通道恢复。

此致、

Ulrich

Hi Kobayashi-San,

由 UCC28070控制的两个相位是独立的升压通道、试图调节到常见输出电压(VSENSE)和常见输入电流基准信号(V_IMO)。 振荡器块只是以相同的频率但是180度异相运行两个相位。

无论交流+侧占空比是大于50%还是小于50%、都没有关系。 就电流检测输入(CSA 或 CSB)而言、交流侧具有负电流、并且由于电流环路无法响应 CSx 的负电压、因此交流侧电流环路将始终具有最大占空比、每个开关周期都会生成最小 Toff 周期。 这种行为是不可避免的、无法更改。

IC 专为传统升压 PFC 的两相交错而设计。 使用此器件控制半桥无 PFC 是 IC 针对拓扑进行的调整。 IC 不"知道"它正在半桥配置中使用。 每个 GDX 输出只需 根据每个通道(相位)的输入进行驱动。

此致、

Ulrich

Hi Kobayashi-San,

您的图表正确。

尽管这种拓扑是无桥的、但考虑传统的整流升压 PFC 可能有用、其中二极管桥后面的电压会进行整流。 在半桥模式下、来自交流波形一半的功率由 A 相(PWM 由 GDA 处理)处理、B 相(GDB)始终处于最大占空比。

在 交流波形的另一半期间、电源由 B 相(PWM 由 GDB 处理)处理、而 A 相(GDA)始终处于最大占空比。

这是我试图传达的信息。 占空比是<50%还是>50%都无关紧要、只有一相在一半的交流周期内处理功率、而另一相在另一个交流半周期内处理功率。 不处理任何功率的相位始终处于 dmax、Toff 最小。

此致、

Ulrich

Hi Kobayashi-San,

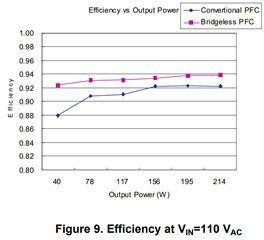

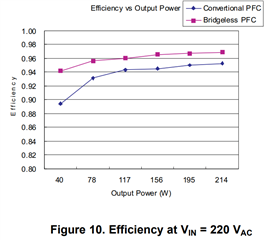

以下效率 图可在本应用 报告中的300W 半桥 ts 设计上找到:https://www.ti.com/lit/an/slua517/slua517.pdf?PFC=1731677853232&ref_url=https%253A%252F%252Fwww.google.com%252F

我希望您的设计能够在无需额外设计工作的情况下也能达到类似的效率水平、即使是在更高的功率下也是如此。

此300W 设计应具有与您在设计中测量的波形类型相同。

如果您的实际效率明显低于如上所示、我建议遵循高电流路径并分析每个电源处理组件中的损耗、以可能改进设计。 例如、可能电感器中的磁芯损耗过大、或者可以改用 SiC 二极管来降低输出二极管中的反向恢复损耗。

如果您的效率已经与上述相似、并且您希望进一步提高效率、那么您列出的想法可能会有所帮助、尤其是增加 L 值以降低 ΔI。 并寻找逐渐降低每个元件损耗的方法。

我不确定添加一个低 Vf 二极管与每个较低的 MOSFET 并联是否能提供大幅改善、但您当然可以尝试一下、看看会发生什么情况。

我还建议尝试 将一个低 Vf 二极管与每个较低输入桥二极管并联、或代替它们。

此致、

Ulrich

Hi Kobayashi-San,

无论输入是高压线还是低压线、体二极管的导通周期都是相同的。 在110Vac 时、体二极管电流更高、但在总 PFC 损耗中、这是非常小的一部分。 我认为可以忽略不计。

我认为110Vac 输入时的效率较低、主要是因为输入均方根电流是220Vac 输入时的两倍。 因此、所有电阻传导损耗增加约4倍(由于 Irms^2)。

由于开关频率是固定的、Vout 是固定的、因此开关损耗不会随线路电压而显著变化、但导通损耗确实变化很大。

这与 传统的固定频率 CCM-BOOST-PFC 效率行为与线路电压一致。 低压线路的损耗通常比高压线路高。

此致、

Ulrich