Other Parts Discussed in Thread: TLV61070A

工具与软件:

您好、TI 专家

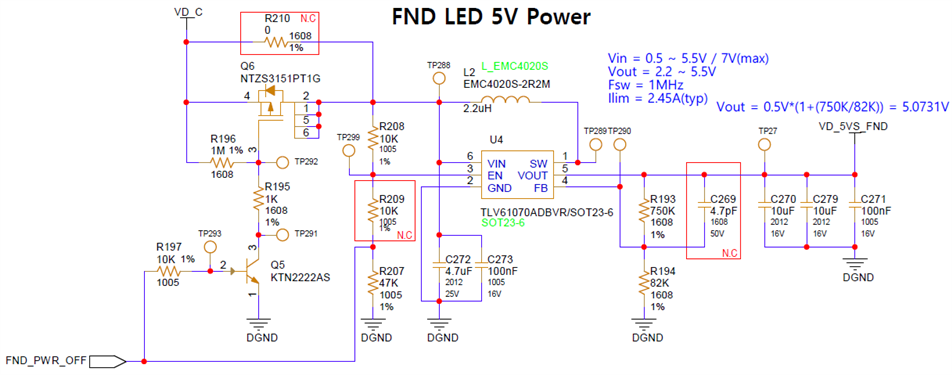

客户通过将 TLV61070A 用作 LED 驱动器的电源来设计该电路板。

不过、会出现功耗在10ms 周期(即 LED 工作周期)内显著下降的现象。

增加输入/输出电容值的容量或调整前馈电容值不会改善该情况。

您能指导我如何改进上述问题吗?

[原理图]

[波形]

请检查。 谢谢你。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好、Travis

感谢您的答复。

信息已传达给客户、客户确认的信息如下。

-据说3.3V~6V 的电压通过串联1.5V 电池进入 TLV76733 (TI)_LDO、TLV76733的输出3.3V 进入 TLV61070A 的 Vin。

-当电路图上的 FND_PWR_OFF 端子关闭时,波形被清除,但当 FND_PWR_OFF 端子打开时,会出现上述现象。

-似乎负载有影响,因为下降发生更多的负载增加。

Q1)与 TLV61070A 的器件功能模式的内容是否相关?

Q2)或是否有任何可能导致上述现象的部分?

Q3)客户私下请求审查电路图和 PCB 布局。 如果您回复私人 E2E 或我的电子邮件(grady.lee@arrow.com)、我将向您发送原理图和 PCB 布局。 您能评论一下吗?

(我将使用 TLV76733创建一个与 Vin 相关的主题、并提出其他问题。)

请检查。 谢谢你。