Part Number: TMS320F28386D-Q1

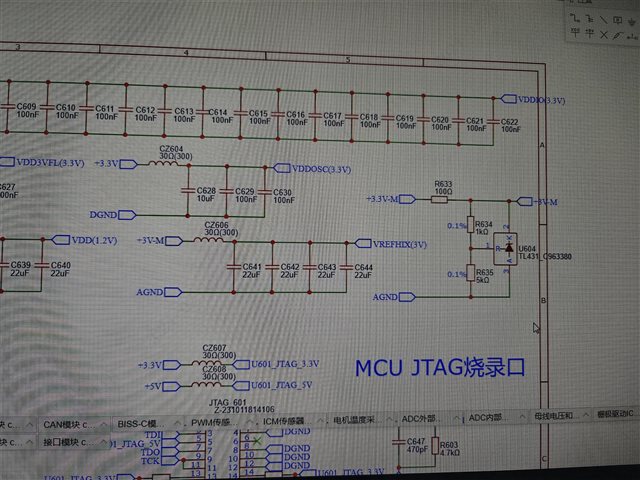

Other Parts Discussed in Thread: TL431

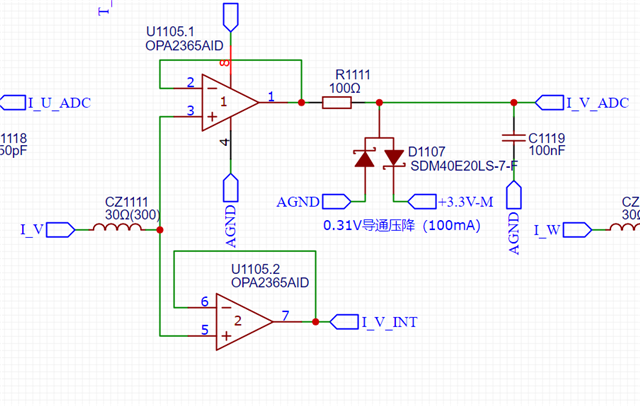

1,通过TL431电压基准芯片转换得到基准电压3V,示波器的测试基准电压纹波Vpp约3.5mV;

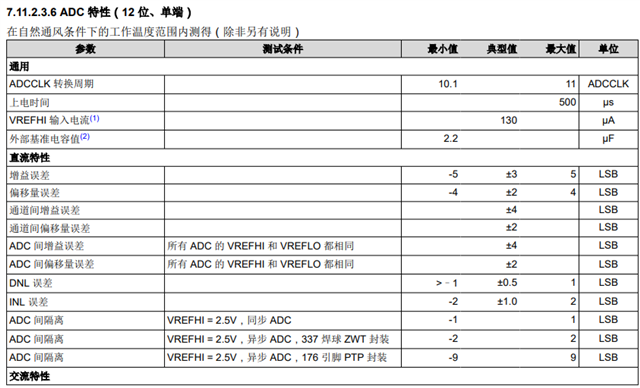

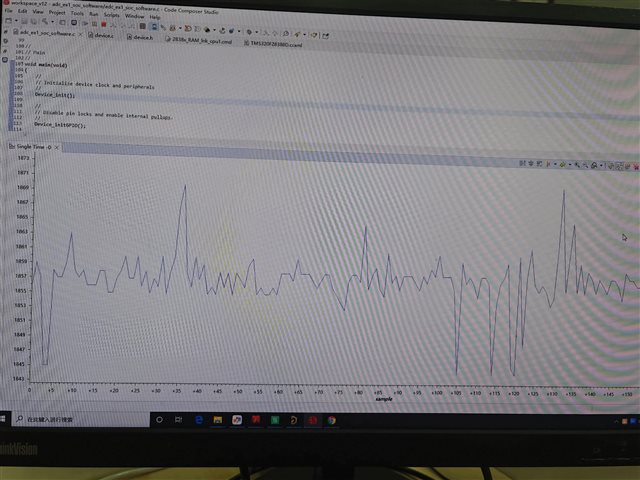

2,单端ADC模式,12BIT,未作后处理;

3,ACQPS尝试过设置为15,64,240,500等,均会无改善;

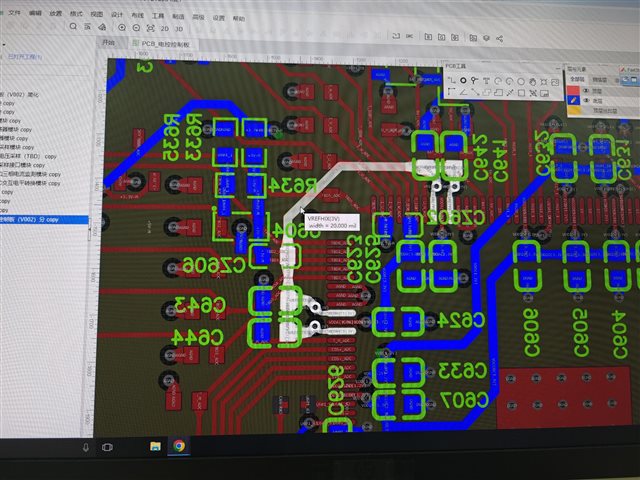

4,运放与DSP芯片之间串接电阻Rs取值100欧姆,Cs电容用过10nF和100nF等,均无改善;

5,尝试DAC输出,测试DAC管脚输出电压纹波Vpp约3mV左右;

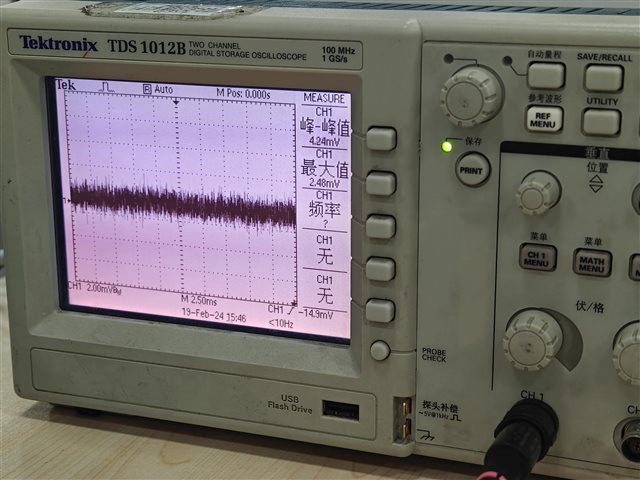

6,示波器测试ADC管脚值纹波Vpp约5mV左右;

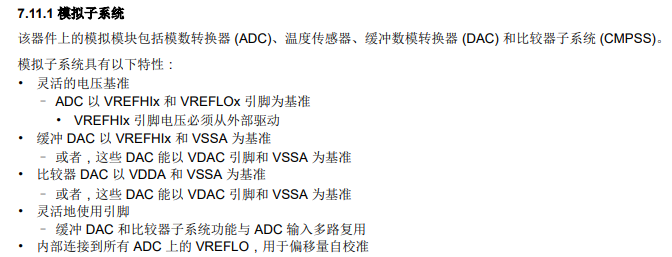

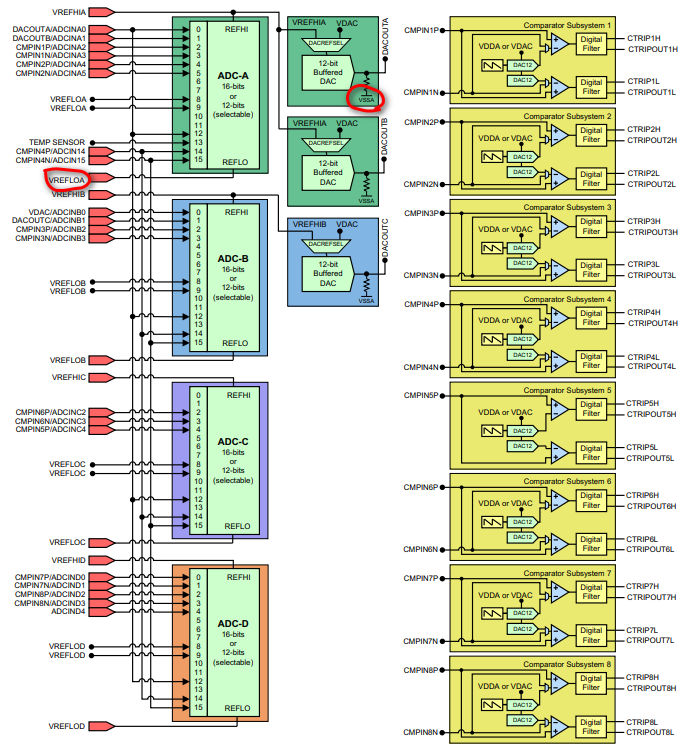

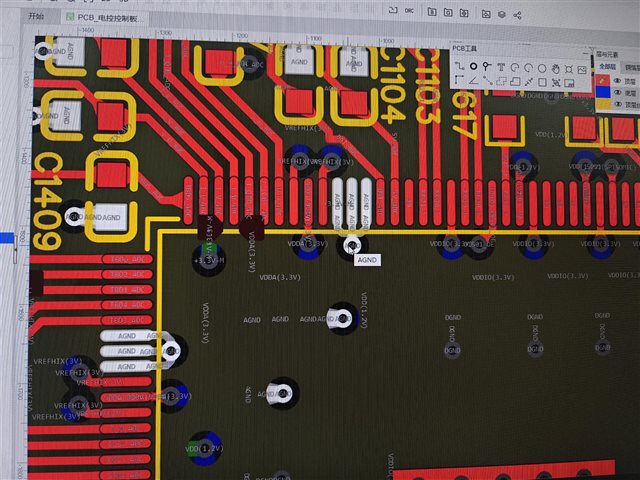

7,VREFLO与线路板AGND连接在一起;

ADC输入电路

参考基准电压电路

参考电压PCB走线

参考地与模拟地直连

检测到的ADC值,未经处理

ADC引脚电压纹波

请帮忙分析有哪些可能的原因会导致采集值跳变到30LSB?